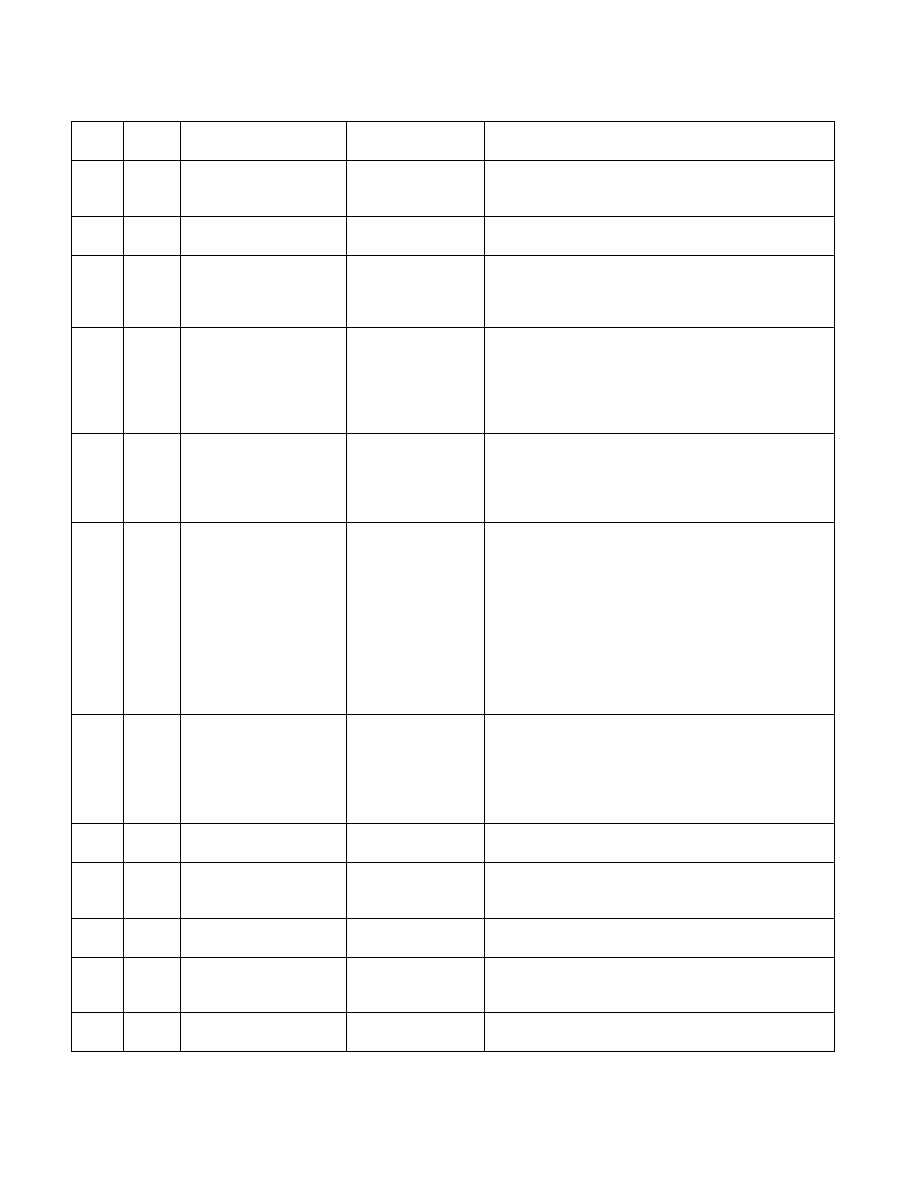

Vol. 3B 19-131

PERFORMANCE-MONITORING EVENTS

82H

40H

ITLB.FLUSH

ITLB flushes.

This event counts the number of ITLB flushes. This usually

happens upon CR3 or CR0 writes, which are executed by

the operating system during process switches.

82

H

12

H

ITLB.MISSES

ITLB misses.

This event counts the number of instruction fetches from

either small or large pages that miss the ITLB.

83

H

02

H

INST_QUEUE.FULL

Cycles during which

the instruction queue

is full.

This event counts the number of cycles during which the

instruction queue is full. In this situation, the core front end

stops fetching more instructions. This is an indication of

very long stalls in the back-end pipeline stages.

86

H

00

H

CYCLES_L1I_

MEM_STALLED

Cycles during which

instruction fetches

stalled.

This event counts the number of cycles for which an

instruction fetch stalls, including stalls due to any of the

following reasons:

• Instruction Fetch Unit cache misses.

• Instruction TLB misses.

• Instruction TLB faults.

87

H

00

H

ILD_STALL

Instruction Length

Decoder stall cycles

due to a length

changing prefix.

This event counts the number of cycles during which the

instruction length decoder uses the slow length decoder.

Usually, instruction length decoding is done in one cycle.

When the slow decoder is used, instruction decoding

requires 6 cycles.

The slow decoder is used in the following cases:

• Operand override prefix (66H) preceding an instruction

with immediate data.

• Address override prefix (67H) preceding an instruction

with a modr/m in real, big real, 16-bit protected or 32-bit

protected modes.

To avoid instruction length decoding stalls, generate code

using imm8 or imm32 values instead of imm16 values. If

you must use an imm16 value, store the value in a register

using “mov reg, imm32” and use the register format of the

instruction.

88H

00H

BR_INST_EXEC

Branch instructions

executed.

This event counts all executed branches (not necessarily

retired). This includes only instructions and not micro-op

branches.

Frequent branching is not necessarily a major performance

issue. However frequent branch mispredictions may be a

problem.

89H

00H

BR_MISSP_EXEC

Mispredicted branch

instructions executed.

This event counts the number of mispredicted branch

instructions that were executed.

8AH

00H

BR_BAC_

MISSP_EXEC

Branch instructions

mispredicted at

decoding.

This event counts the number of branch instructions that

were mispredicted at decoding.

8BH

00H

BR_CND_EXEC

Conditional branch

instructions executed.

This event counts the number of conditional branch

instructions executed, but not necessarily retired.

8CH

00H

BR_CND_

MISSP_EXEC

Mispredicted

conditional branch

instructions executed.

This event counts the number of mispredicted conditional

branch instructions that were executed.

8DH

00H

BR_IND_EXEC

Indirect branch

instructions executed.

This event counts the number of indirect branch instructions

that were executed.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment