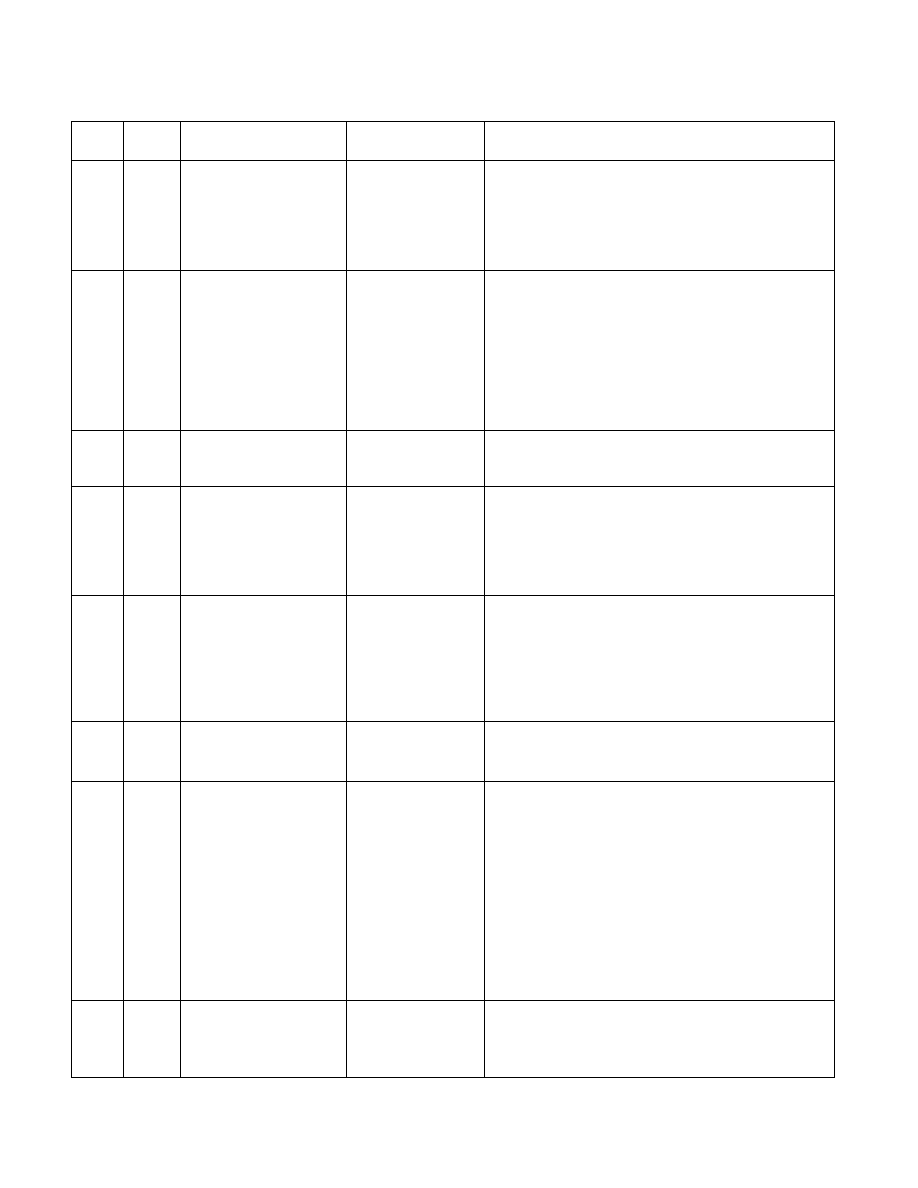

Vol. 3B 19-121

PERFORMANCE-MONITORING EVENTS

08

H

08

H

DTLB_MISSES.

MISS_ST

TLB misses due to

store operations.

This event counts the number of Data Table Lookaside

Buffer (DTLB) misses due to store operations.

This count includes misses detected as a result of

speculative accesses. Address translation for store

operations is performed in the DTLB1.

09H

01H

MEMORY_

DISAMBIGUATION.RESET

Memory

disambiguation reset

cycles.

This event counts the number of cycles during which

memory disambiguation misprediction occurs. As a result

the execution pipeline is cleaned and execution of the

mispredicted load instruction and all succeeding instructions

restarts.

This event occurs when the data address accessed by a load

instruction, collides infrequently with preceding stores, but

usually there is no collision. It happens rarely, and may have

a penalty of about 20 cycles.

09H

02H

MEMORY_DISAMBIGUATIO

N.SUCCESS

Number of loads

successfully

disambiguated.

This event counts the number of load operations that were

successfully disambiguated. Loads are preceded by a store

with an unknown address, but they are not blocked.

0C

H

01

H

PAGE_WALKS

.COUNT

Number of page-walks

executed.

This event counts the number of page-walks executed due

to either a DTLB or ITLB miss.

The page walk duration, PAGE_WALKS.CYCLES, divided by

number of page walks is the average duration of a page

walk. The average can hint whether most of the page-walks

are satisfied by the caches or cause an L2 cache miss.

0C

H

02

H

PAGE_WALKS.

CYCLES

Duration of page-

walks in core cycles.

This event counts the duration of page-walks in core cycles.

The paging mode in use typically affects the duration of

page walks.

Page walk duration divided by number of page walks is the

average duration of page-walks. The average can hint at

whether most of the page-walks are satisfied by the caches

or cause an L2 cache miss.

10

H

00

H

FP_COMP_OPS

_EXE

Floating point

computational micro-

ops executed.

This event counts the number of floating point

computational micro-ops executed.

Use IA32_PMC0 only.

11

H

00

H

FP_ASSIST

Floating point assists. This event counts the number of floating point operations

executed that required micro-code assist intervention.

Assists are required in the following cases:

• Streaming SIMD Extensions (SSE) instructions:

• Denormal input when the DAZ (Denormals Are Zeros) flag

is off

• Underflow result when the FTZ (Flush To Zero) flag is off

• X87 instructions:

• NaN or denormal are loaded to a register or used as input

from memory

• Division by 0

• Underflow output

Use IA32_PMC1 only.

12

H

00

H

MUL

Multiply operations

executed.

This event counts the number of multiply operations

executed. This includes integer as well as floating point

multiply operations.

Use IA32_PMC1 only.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment