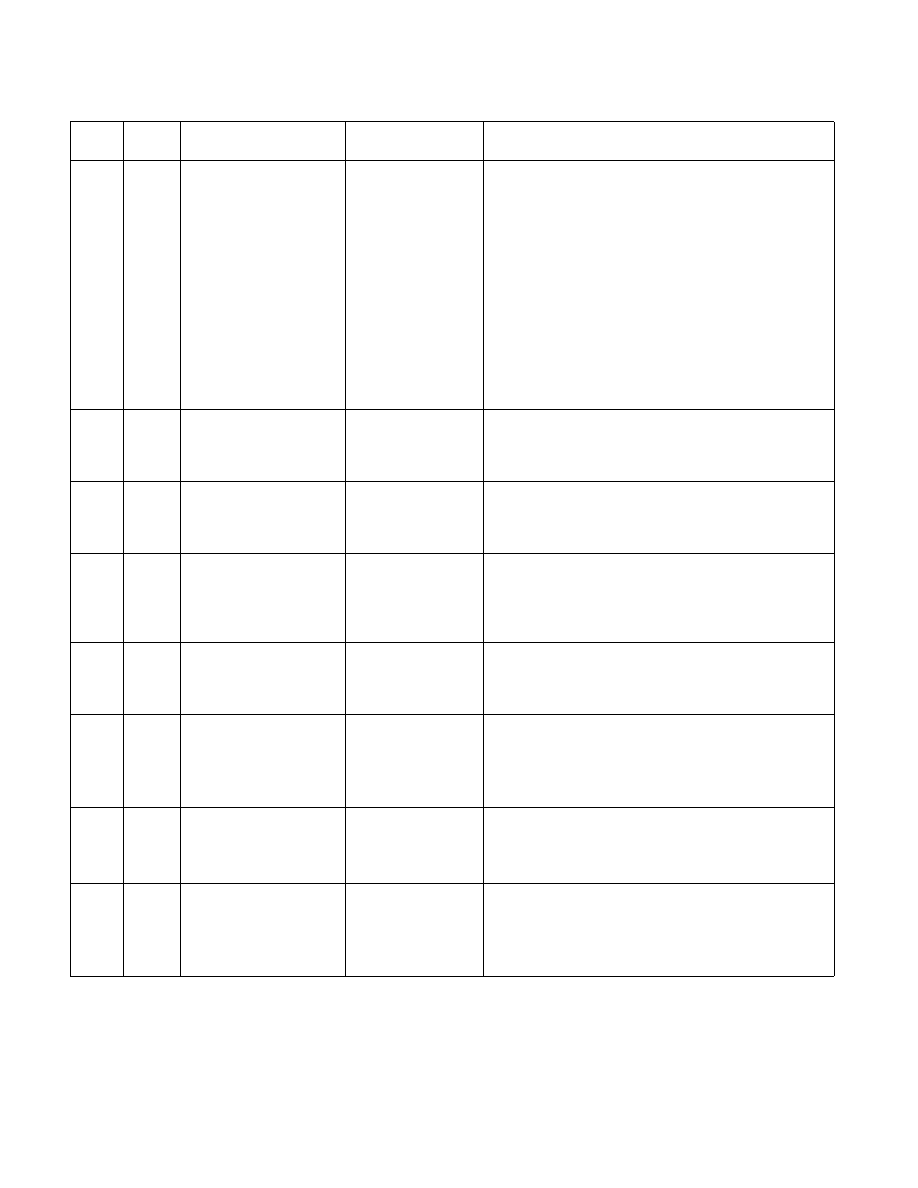

19-120 Vol. 3B

PERFORMANCE-MONITORING EVENTS

06

H

00

H

SEGMENT_REG_

LOADS

Number of segment

register loads.

This event counts the number of segment register load

operations. Instructions that load new values into segment

registers cause a penalty.

This event indicates performance issues in 16-bit code. If

this event occurs frequently, it may be useful to calculate

the number of instructions retired per segment register

load. If the resulting calculation is low (on average a small

number of instructions are executed between segment

register loads), then the code’s segment register usage

should be optimized.

As a result of branch misprediction, this event is speculative

and may include segment register loads that do not actually

occur. However, most segment register loads are internally

serialized and such speculative effects are minimized.

07

H

00

H

SSE_PRE_EXEC.

NTA

Streaming SIMD

Extensions (SSE)

Prefetch NTA

instructions executed.

This event counts the number of times the SSE instruction

prefetchNTA is executed.

This instruction prefetches the data to the L1 data cache.

07

H

01

H

SSE_PRE_EXEC.L1

Streaming SIMD

Extensions (SSE)

PrefetchT0

instructions executed.

This event counts the number of times the SSE instruction

prefetchT0 is executed. This instruction prefetches the data

to the L1 data cache and L2 cache.

07

H

02

H

SSE_PRE_EXEC.L2

Streaming SIMD

Extensions (SSE)

PrefetchT1 and

PrefetchT2

instructions executed.

This event counts the number of times the SSE instructions

prefetchT1 and prefetchT2 are executed. These

instructions prefetch the data to the L2 cache.

07H

03H

SSE_PRE_

EXEC.STORES

Streaming SIMD

Extensions (SSE)

Weakly-ordered store

instructions executed.

This event counts the number of times SSE non-temporal

store instructions are executed.

08

H

01

H

DTLB_MISSES.

ANY

Memory accesses that

missed the DTLB.

This event counts the number of Data Table Lookaside

Buffer (DTLB) misses. The count includes misses detected

as a result of speculative accesses.

Typically a high count for this event indicates that the code

accesses a large number of data pages.

08

H

02

H

DTLB_MISSES

.MISS_LD

DTLB misses due to

load operations.

This event counts the number of Data Table Lookaside

Buffer (DTLB) misses due to load operations.

This count includes misses detected as a result of

speculative accesses.

08

H

04

H

DTLB_MISSES.L0_MISS_LD L0 DTLB misses due to

load operations.

This event counts the number of level 0 Data Table

Lookaside Buffer (DTLB0) misses due to load operations.

This count includes misses detected as a result of

speculative accesses. Loads that miss that DTLB0 and hit

the DTLB1 can incur two-cycle penalty.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment