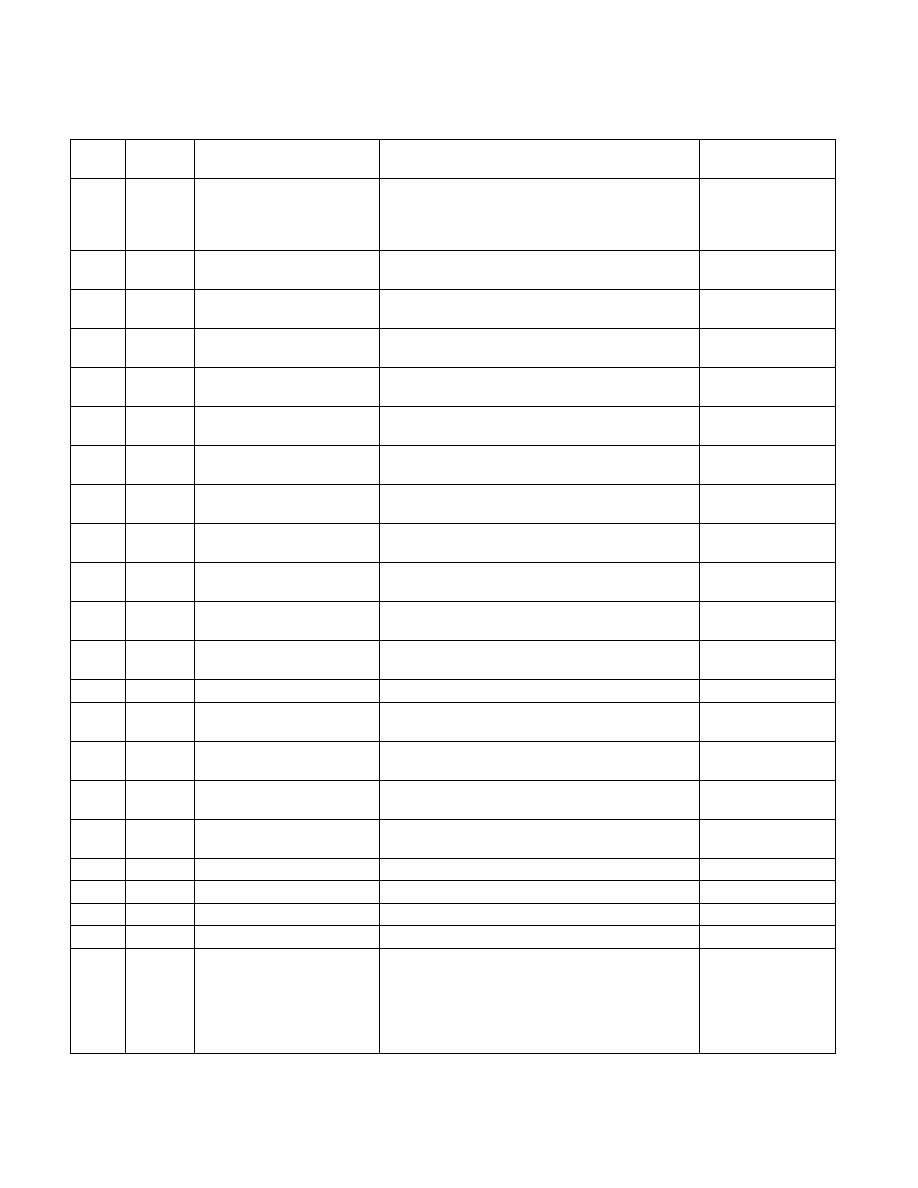

Vol. 3B 19-109

PERFORMANCE-MONITORING EVENTS

2CH

07H

UNC_QMC_NORMAL_READS.A

NY

Counts the number of Quickpath Memory Controller

medium and low priority read requests. The QMC

normal read occupancy divided by this count provides

the average QMC read latency.

2DH

01H

UNC_QMC_HIGH_PRIORITY_RE

ADS.CH0

Counts the number of Quickpath Memory Controller

channel 0 high priority isochronous read requests.

2DH

02H

UNC_QMC_HIGH_PRIORITY_RE

ADS.CH1

Counts the number of Quickpath Memory Controller

channel 1 high priority isochronous read requests.

2DH

04H

UNC_QMC_HIGH_PRIORITY_RE

ADS.CH2

Counts the number of Quickpath Memory Controller

channel 2 high priority isochronous read requests.

2DH

07H

UNC_QMC_HIGH_PRIORITY_RE

ADS.ANY

Counts the number of Quickpath Memory Controller

high priority isochronous read requests.

2EH

01H

UNC_QMC_CRITICAL_PRIORITY

_READS.CH0

Counts the number of Quickpath Memory Controller

channel 0 critical priority isochronous read requests.

2EH

02H

UNC_QMC_CRITICAL_PRIORITY

_READS.CH1

Counts the number of Quickpath Memory Controller

channel 1 critical priority isochronous read requests.

2EH

04H

UNC_QMC_CRITICAL_PRIORITY

_READS.CH2

Counts the number of Quickpath Memory Controller

channel 2 critical priority isochronous read requests.

2EH

07H

UNC_QMC_CRITICAL_PRIORITY

_READS.ANY

Counts the number of Quickpath Memory Controller

critical priority isochronous read requests.

2FH

01H

UNC_QMC_WRITES.FULL.CH0

Counts number of full cache line writes to DRAM

channel 0.

2FH

02H

UNC_QMC_WRITES.FULL.CH1

Counts number of full cache line writes to DRAM

channel 1.

2FH

04H

UNC_QMC_WRITES.FULL.CH2

Counts number of full cache line writes to DRAM

channel 2.

2FH

07H

UNC_QMC_WRITES.FULL.ANY

Counts number of full cache line writes to DRAM.

2FH

08H

UNC_QMC_WRITES.PARTIAL.C

H0

Counts number of partial cache line writes to DRAM

channel 0.

2FH

10H

UNC_QMC_WRITES.PARTIAL.C

H1

Counts number of partial cache line writes to DRAM

channel 1.

2FH

20H

UNC_QMC_WRITES.PARTIAL.C

H2

Counts number of partial cache line writes to DRAM

channel 2.

2FH

38H

UNC_QMC_WRITES.PARTIAL.A

NY

Counts number of partial cache line writes to DRAM.

30H

01H

UNC_QMC_CANCEL.CH0

Counts number of DRAM channel 0 cancel requests.

30H

02H

UNC_QMC_CANCEL.CH1

Counts number of DRAM channel 1 cancel requests.

30H

04H

UNC_QMC_CANCEL.CH2

Counts number of DRAM channel 2 cancel requests.

30H

07H

UNC_QMC_CANCEL.ANY

Counts number of DRAM cancel requests.

31H

01H

UNC_QMC_PRIORITY_UPDATE

S.CH0

Counts number of DRAM channel 0 priority updates. A

priority update occurs when an ISOC high or critical

request is received by the QHL and there is a matching

request with normal priority that has already been

issued to the QMC. In this instance, the QHL will send a

priority update to QMC to expedite the request.

Table 19-20. Non-Architectural Performance Events In the Processor Uncore for

Processors Based on Intel® Microarchitecture Code Name Westmere (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment