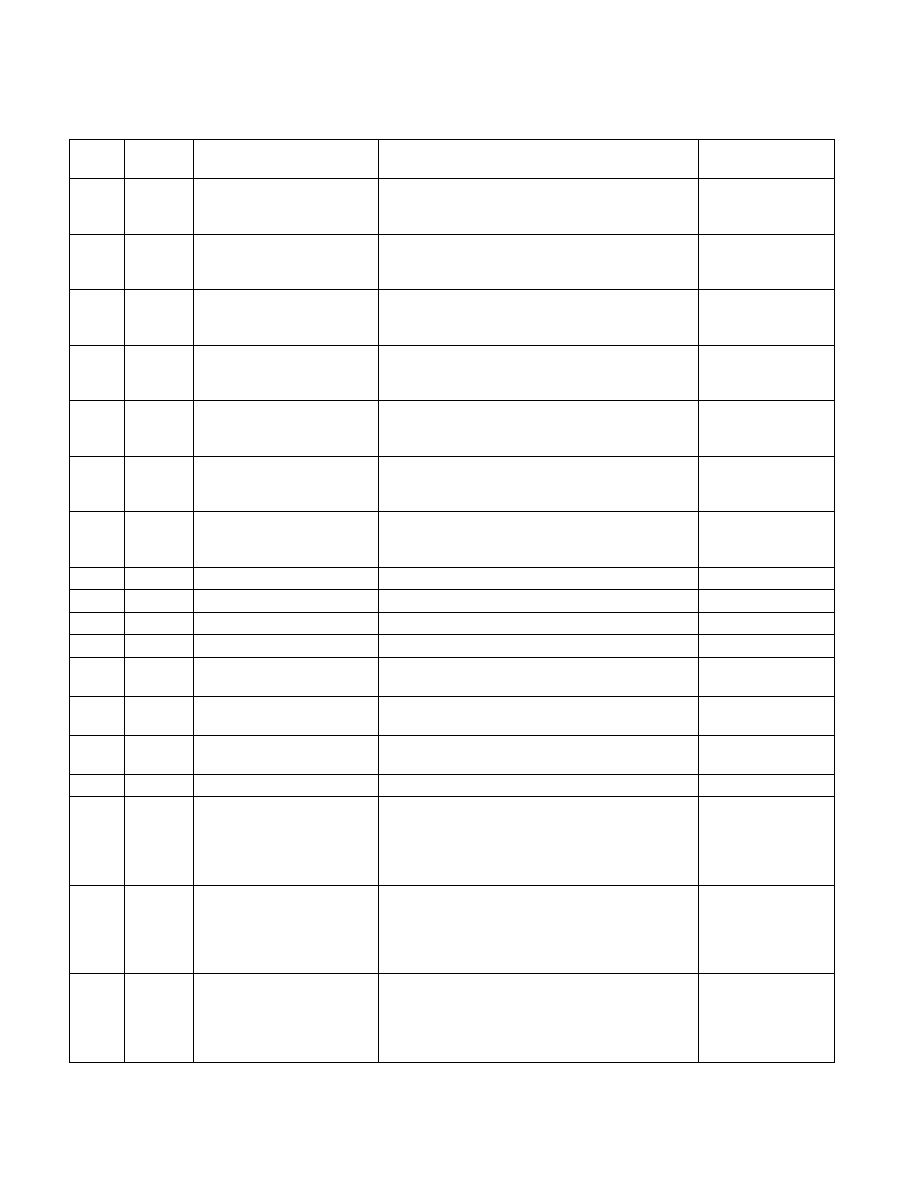

19-108 Vol. 3B

PERFORMANCE-MONITORING EVENTS

28H

20H

UNC_QMC_ISOC_FULL.WRITE.C

H2

Counts cycles all the entries in the DRAM channel 2

high priority queue are occupied with isochronous

write requests.

29H

01H

UNC_QMC_BUSY.READ.CH0

Counts cycles where Quickpath Memory Controller has

at least 1 outstanding read request to DRAM channel

0.

29H

02H

UNC_QMC_BUSY.READ.CH1

Counts cycles where Quickpath Memory Controller has

at least 1 outstanding read request to DRAM channel

1.

29H

04H

UNC_QMC_BUSY.READ.CH2

Counts cycles where Quickpath Memory Controller has

at least 1 outstanding read request to DRAM channel

2.

29H

08H

UNC_QMC_BUSY.WRITE.CH0

Counts cycles where Quickpath Memory Controller has

at least 1 outstanding write request to DRAM channel

0.

29H

10H

UNC_QMC_BUSY.WRITE.CH1

Counts cycles where Quickpath Memory Controller has

at least 1 outstanding write request to DRAM channel

1.

29H

20H

UNC_QMC_BUSY.WRITE.CH2

Counts cycles where Quickpath Memory Controller has

at least 1 outstanding write request to DRAM channel

2.

2AH

01H

UNC_QMC_OCCUPANCY.CH0

IMC channel 0 normal read request occupancy.

2AH

02H

UNC_QMC_OCCUPANCY.CH1

IMC channel 1 normal read request occupancy.

2AH

04H

UNC_QMC_OCCUPANCY.CH2

IMC channel 2 normal read request occupancy.

2AH

07H

UNC_QMC_OCCUPANCY.ANY

Normal read request occupancy for any channel.

2BH

01H

UNC_QMC_ISSOC_OCCUPANCY.

CH0

IMC channel 0 issoc read request occupancy.

2BH

02H

UNC_QMC_ISSOC_OCCUPANCY.

CH1

IMC channel 1 issoc read request occupancy.

2BH

04H

UNC_QMC_ISSOC_OCCUPANCY.

CH2

IMC channel 2 issoc read request occupancy.

2BH

07H

UNC_QMC_ISSOC_READS.ANY IMC issoc read request occupancy.

2CH

01H

UNC_QMC_NORMAL_READS.C

H0

Counts the number of Quickpath Memory Controller

channel 0 medium and low priority read requests. The

QMC channel 0 normal read occupancy divided by this

count provides the average QMC channel 0 read

latency.

2CH

02H

UNC_QMC_NORMAL_READS.C

H1

Counts the number of Quickpath Memory Controller

channel 1 medium and low priority read requests. The

QMC channel 1 normal read occupancy divided by this

count provides the average QMC channel 1 read

latency.

2CH

04H

UNC_QMC_NORMAL_READS.C

H2

Counts the number of Quickpath Memory Controller

channel 2 medium and low priority read requests. The

QMC channel 2 normal read occupancy divided by this

count provides the average QMC channel 2 read

latency.

Table 19-20. Non-Architectural Performance Events In the Processor Uncore for

Processors Based on Intel® Microarchitecture Code Name Westmere (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment