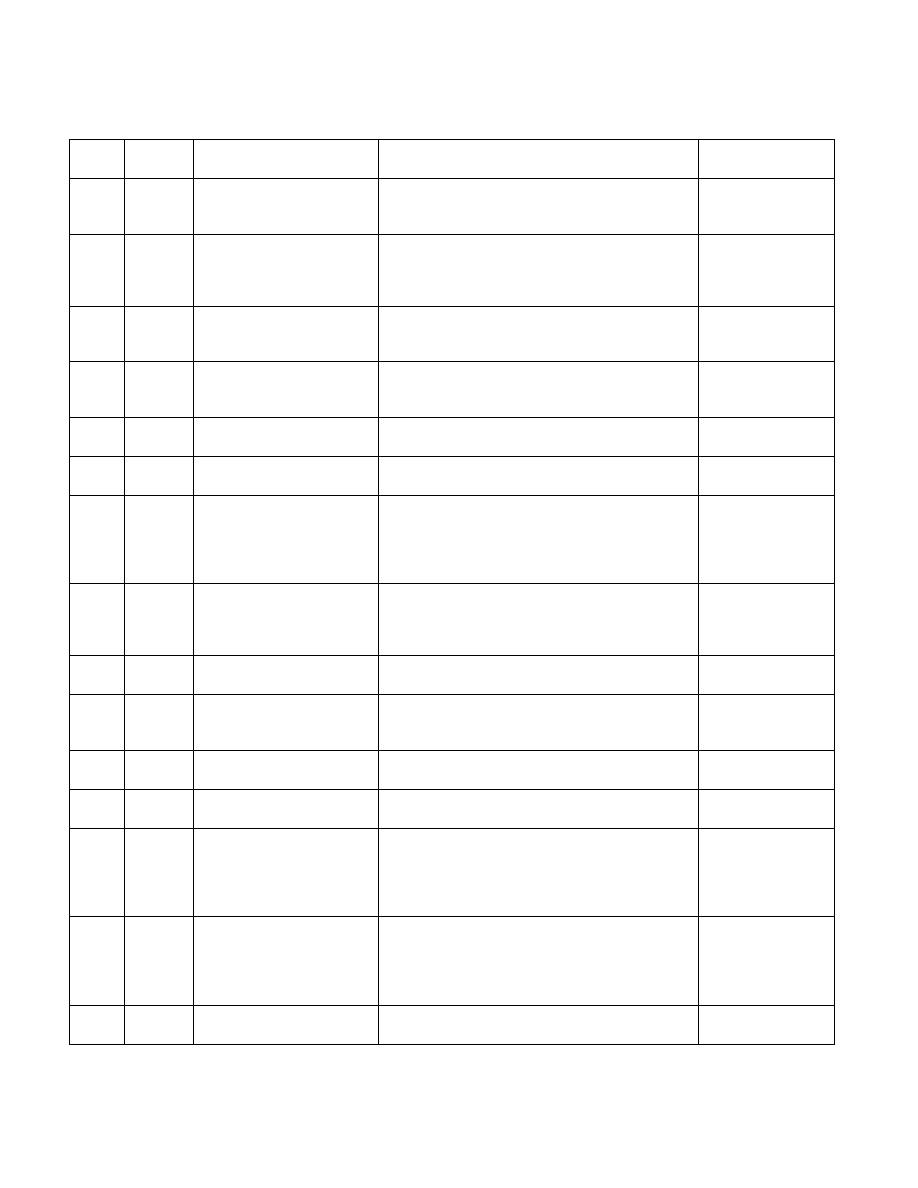

19-104 Vol. 3B

PERFORMANCE-MONITORING EVENTS

04H

10H

UNC_GQ_DATA.FROM_CORES_

13

Cycles GQ Core 1 and 3 input data port is busy

importing data from processor cores 1 and 3. Each

cycle the input port can transfer 32 bytes of data.

05H

01H

UNC_GQ_DATA.TO_QPI_QMC

Cycles GQ QPI and QMC output data port is busy

sending data to the Quickpath Interface or Quickpath

Memory Interface. Each cycle the output port can

transfer 32 bytes of data.

05H

02H

UNC_GQ_DATA.TO_L3

Cycles GQ L3 output data port is busy sending data to

the Last Level Cache. Each cycle the output port can

transfer 32 bytes of data.

05H

04H

UNC_GQ_DATA.TO_CORES

Cycles GQ Core output data port is busy sending data

to the Cores. Each cycle the output port can transfer

32 bytes of data.

06H

01H

UNC_SNP_RESP_TO_LOCAL_H

OME.I_STATE

Number of snoop responses to the local home that L3

does not have the referenced cache line.

06H

02H

UNC_SNP_RESP_TO_LOCAL_H

OME.S_STATE

Number of snoop responses to the local home that L3

has the referenced line cached in the S state.

06H

04H

UNC_SNP_RESP_TO_LOCAL_H

OME.FWD_S_STATE

Number of responses to code or data read snoops to

the local home that the L3 has the referenced cache

line in the E state. The L3 cache line state is changed

to the S state and the line is forwarded to the local

home in the S state.

06H

08H

UNC_SNP_RESP_TO_LOCAL_H

OME.FWD_I_STATE

Number of responses to read invalidate snoops to the

local home that the L3 has the referenced cache line in

the M state. The L3 cache line state is invalidated and

the line is forwarded to the local home in the M state.

06H

10H

UNC_SNP_RESP_TO_LOCAL_H

OME.CONFLICT

Number of conflict snoop responses sent to the local

home.

06H

20H

UNC_SNP_RESP_TO_LOCAL_H

OME.WB

Number of responses to code or data read snoops to

the local home that the L3 has the referenced line

cached in the M state.

07H

01H

UNC_SNP_RESP_TO_REMOTE_

HOME.I_STATE

Number of snoop responses to a remote home that L3

does not have the referenced cache line.

07H

02H

UNC_SNP_RESP_TO_REMOTE_

HOME.S_STATE

Number of snoop responses to a remote home that L3

has the referenced line cached in the S state.

07H

04H

UNC_SNP_RESP_TO_REMOTE_

HOME.FWD_S_STATE

Number of responses to code or data read snoops to a

remote home that the L3 has the referenced cache

line in the E state. The L3 cache line state is changed

to the S state and the line is forwarded to the remote

home in the S state.

07H

08H

UNC_SNP_RESP_TO_REMOTE_

HOME.FWD_I_STATE

Number of responses to read invalidate snoops to a

remote home that the L3 has the referenced cache

line in the M state. The L3 cache line state is

invalidated and the line is forwarded to the remote

home in the M state.

07H

10H

UNC_SNP_RESP_TO_REMOTE_

HOME.CONFLICT

Number of conflict snoop responses sent to the local

home.

Table 19-20. Non-Architectural Performance Events In the Processor Uncore for

Processors Based on Intel® Microarchitecture Code Name Westmere (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment