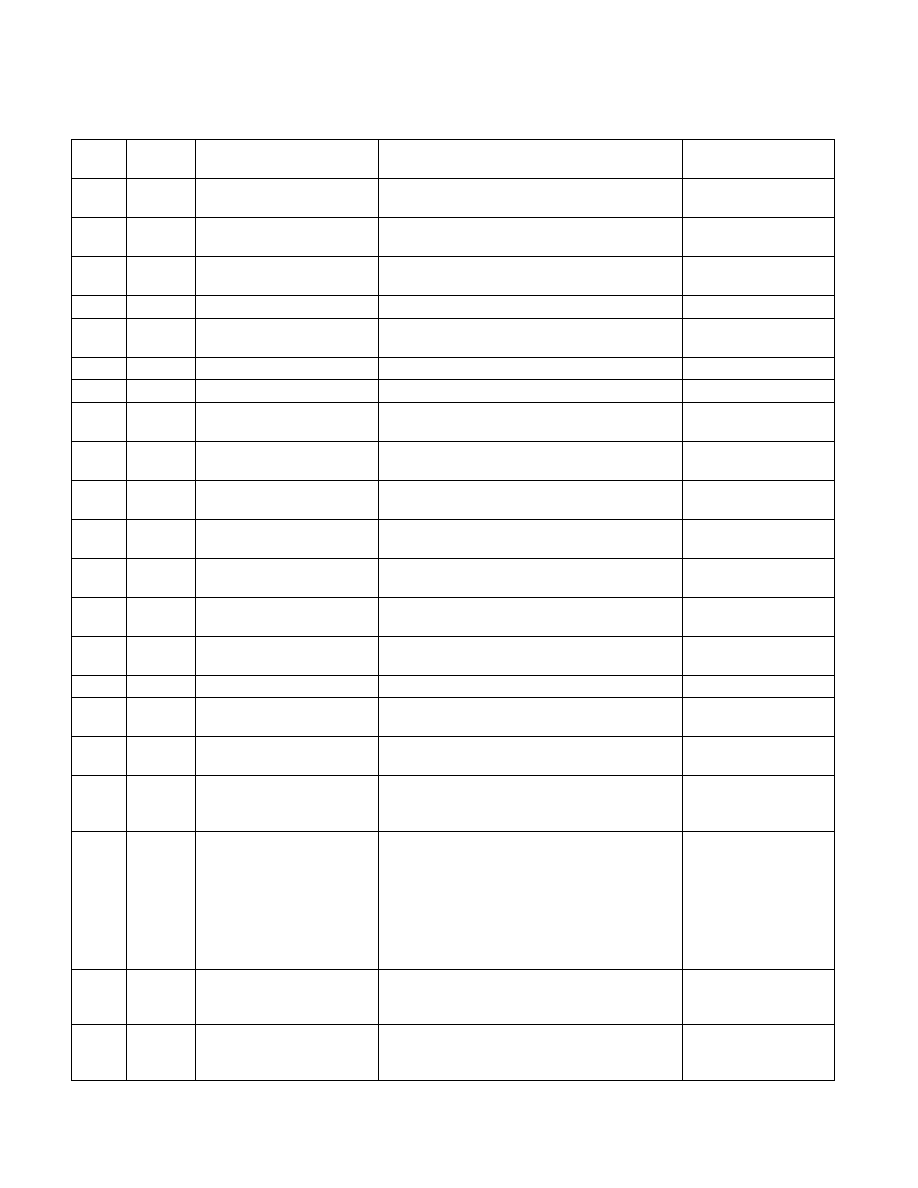

Vol. 3B 19-101

PERFORMANCE-MONITORING EVENTS

F0H

02H

L2_TRANSACTIONS.RFO

Counts L2 RFO operations due to HW prefetch or

demand RFOs.

F0H

04H

L2_TRANSACTIONS.IFETCH

Counts L2 instruction fetch operations due to HW

prefetch or demand ifetch.

F0H

08H

L2_TRANSACTIONS.PREFETC

H

Counts L2 prefetch operations.

F0H

10H

L2_TRANSACTIONS.L1D_WB

Counts L1D writeback operations to the L2.

F0H

20H

L2_TRANSACTIONS.FILL

Counts L2 cache line fill operations due to load, RFO,

L1D writeback or prefetch.

F0H

40H

L2_TRANSACTIONS.WB

Counts L2 writeback operations to the L3.

F0H

80H

L2_TRANSACTIONS.ANY

Counts all L2 cache operations.

F1H

02H

L2_LINES_IN.S_STATE

Counts the number of cache lines allocated in the L2

cache in the S (shared) state.

F1H

04H

L2_LINES_IN.E_STATE

Counts the number of cache lines allocated in the L2

cache in the E (exclusive) state.

F1H

07H

L2_LINES_IN.ANY

Counts the number of cache lines allocated in the L2

cache.

F2H

01H

L2_LINES_OUT.DEMAND_CLEA

N

Counts L2 clean cache lines evicted by a demand

request.

F2H

02H

L2_LINES_OUT.DEMAND_DIRT

Y

Counts L2 dirty (modified) cache lines evicted by a

demand request.

F2H

04H

L2_LINES_OUT.PREFETCH_CL

EAN

Counts L2 clean cache line evicted by a prefetch

request.

F2H

08H

L2_LINES_OUT.PREFETCH_DIR

TY

Counts L2 modified cache line evicted by a prefetch

request.

F2H

0FH

L2_LINES_OUT.ANY

Counts all L2 cache lines evicted for any reason.

F4H

04H

SQ_MISC.LRU_HINTS

Counts number of Super Queue LRU hints sent to

L3.

F4H

10H

SQ_MISC.SPLIT_LOCK

Counts the number of SQ lock splits across a cache

line.

F6H

01H

SQ_FULL_STALL_CYCLES

Counts cycles the Super Queue is full. Neither of the

threads on this core will be able to access the

uncore.

F7H

01H

FP_ASSIST.ALL

Counts the number of floating point operations

executed that required micro-code assist

intervention. Assists are required in the following

cases: SSE instructions, (Denormal input when the

DAZ flag is off or Underflow result when the FTZ

flag is off): x87 instructions, (NaN or denormal are

loaded to a register or used as input from memory,

Division by 0 or Underflow output).

F7H

02H

FP_ASSIST.OUTPUT

Counts number of floating point micro-code assist

when the output value (destination register) is

invalid.

F7H

04H

FP_ASSIST.INPUT

Counts number of floating point micro-code assist

when the input value (one of the source operands

to an FP instruction) is invalid.

Table 19-19. Non-Architectural Performance Events In the Processor Core for

Processors Based on Intel® Microarchitecture Code Name Westmere (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment