19-94 Vol. 3B

PERFORMANCE-MONITORING EVENTS

88H

30H

BR_INST_EXEC.NEAR_CALLS

Counts all near call branches executed, but not

necessarily retired.

88H

40H

BR_INST_EXEC.TAKEN

Counts taken near branches executed, but not

necessarily retired.

88H

7FH

BR_INST_EXEC.ANY

Counts all near executed branches (not necessarily

retired). This includes only instructions and not

micro-op branches. Frequent branching is not

necessarily a major performance issue. However

frequent branch mispredictions may be a problem.

89H

01H

BR_MISP_EXEC.COND

Counts the number of mispredicted conditional near

branch instructions executed, but not necessarily

retired.

89H

02H

BR_MISP_EXEC.DIRECT

Counts mispredicted macro unconditional near

branch instructions, excluding calls and indirect

branches (should always be 0).

89H

04H

BR_MISP_EXEC.INDIRECT_NO

N_CALL

Counts the number of executed mispredicted

indirect near branch instructions that are not calls.

89H

07H

BR_MISP_EXEC.NON_CALLS

Counts mispredicted non-call near branches

executed, but not necessarily retired.

89H

08H

BR_MISP_EXEC.RETURN_NEA

R

Counts mispredicted indirect branches that have a

rear return mnemonic.

89H

10H

BR_MISP_EXEC.DIRECT_NEAR

_CALL

Counts mispredicted non-indirect near calls

executed, (should always be 0).

89H

20H

BR_MISP_EXEC.INDIRECT_NE

AR_CALL

Counts mispredicted indirect near calls executed,

including both register and memory indirect.

89H

30H

BR_MISP_EXEC.NEAR_CALLS

Counts all mispredicted near call branches executed,

but not necessarily retired.

89H

40H

BR_MISP_EXEC.TAKEN

Counts executed mispredicted near branches that

are taken, but not necessarily retired.

89H

7FH

BR_MISP_EXEC.ANY

Counts the number of mispredicted near branch

instructions that were executed, but not

necessarily retired.

A2H

01H

RESOURCE_STALLS.ANY

Counts the number of Allocator resource related

stalls. Includes register renaming buffer entries,

memory buffer entries. In addition to resource

related stalls, this event counts some other events.

Includes stalls arising during branch misprediction

recovery, such as if retirement of the mispredicted

branch is delayed and stalls arising while store

buffer is draining from synchronizing operations.

Does not include stalls

due to SuperQ (off core)

queue full, too many

cache misses, etc.

A2H

02H

RESOURCE_STALLS.LOAD

Counts the cycles of stall due to lack of load buffer

for load operation.

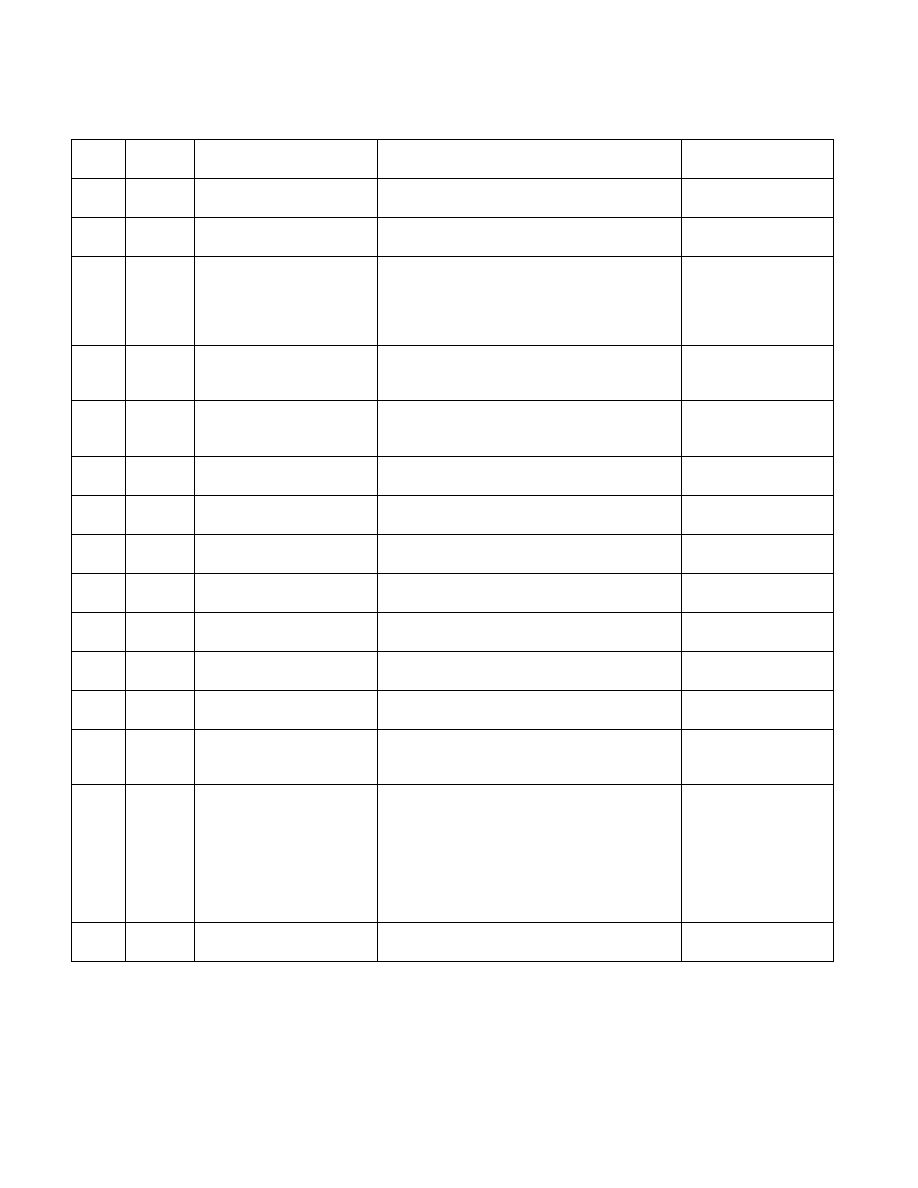

Table 19-19. Non-Architectural Performance Events In the Processor Core for

Processors Based on Intel® Microarchitecture Code Name Westmere (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment