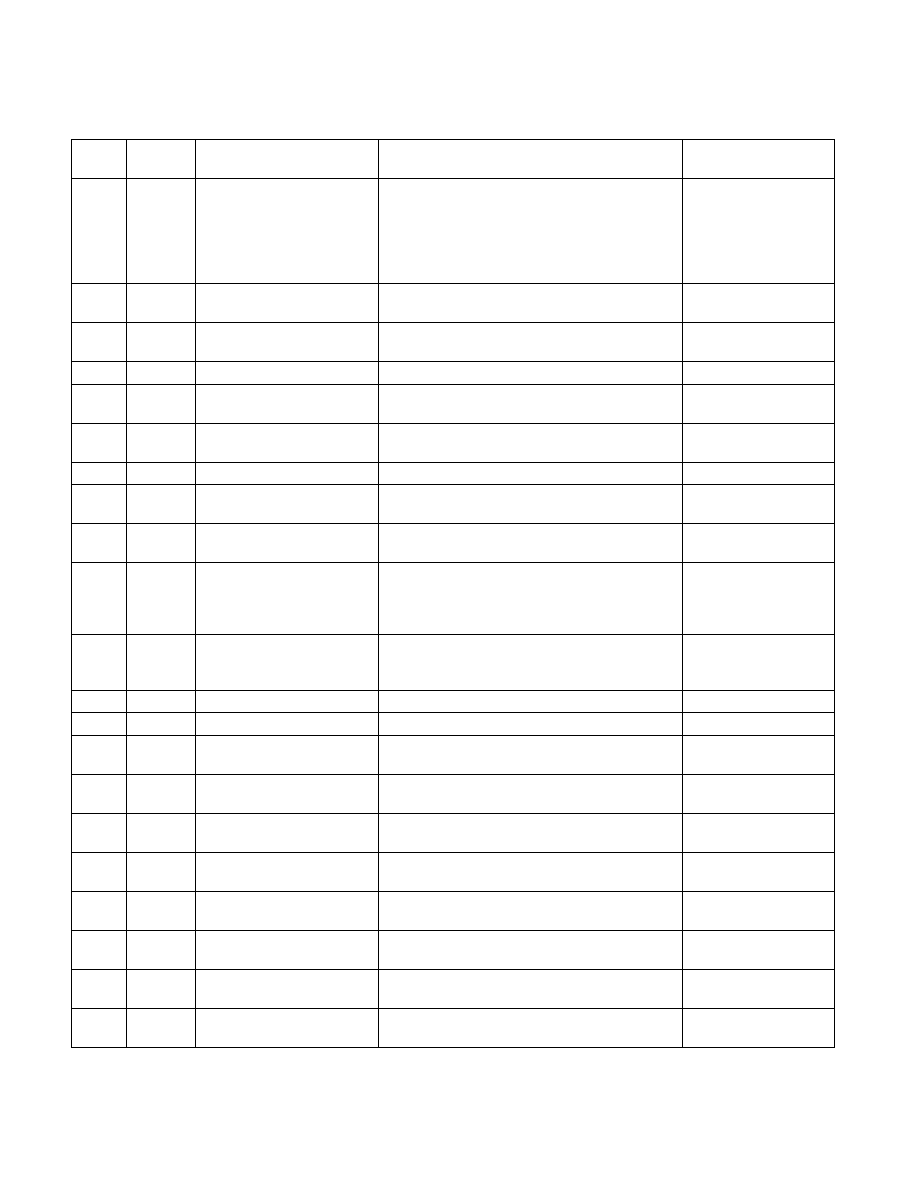

Vol. 3B 19-93

PERFORMANCE-MONITORING EVENTS

80H

02H

L1I.MISSES

Counts all instruction fetches that miss the L1I

cache. This includes instruction cache misses,

streaming buffer misses, victim cache misses and

uncacheable fetches. An instruction fetch miss is

counted only once and not once for every cycle it is

outstanding.

80H

03H

L1I.READS

Counts all instruction fetches, including uncacheable

fetches that bypass the L1I.

80H

04H

L1I.CYCLES_STALLED

Cycle counts for which an instruction fetch stalls

due to a L1I cache miss, ITLB miss or ITLB fault.

82H

01H

LARGE_ITLB.HIT

Counts number of large ITLB hits.

85H

01H

ITLB_MISSES.ANY

Counts the number of misses in all levels of the ITLB

which causes a page walk.

85H

02H

ITLB_MISSES.WALK_COMPLET

ED

Counts number of misses in all levels of the ITLB

which resulted in a completed page walk.

85H

04H

ITLB_MISSES.WALK_CYCLES

Counts ITLB miss page walk cycles.

85H

10H

ITLB_MISSES.STLB_HIT

Counts number of ITLB first level miss but second

level hits.

85H

80H

ITLB_MISSES.LARGE_WALK_C

OMPLETED

Counts number of completed large page walks due

to misses in the STLB.

87H

01H

ILD_STALL.LCP

Cycles Instruction Length Decoder stalls due to

length changing prefixes: 66, 67 or REX.W (for Intel

64) instructions which change the length of the

decoded instruction.

87H

02H

ILD_STALL.MRU

Instruction Length Decoder stall cycles due to Brand

Prediction Unit (PBU) Most Recently Used (MRU)

bypass.

87H

04H

ILD_STALL.IQ_FULL

Stall cycles due to a full instruction queue.

87H

08H

ILD_STALL.REGEN

Counts the number of regen stalls.

87H

0FH

ILD_STALL.ANY

Counts any cycles the Instruction Length Decoder is

stalled.

88H

01H

BR_INST_EXEC.COND

Counts the number of conditional near branch

instructions executed, but not necessarily retired.

88H

02H

BR_INST_EXEC.DIRECT

Counts all unconditional near branch instructions

excluding calls and indirect branches.

88H

04H

BR_INST_EXEC.INDIRECT_NO

N_CALL

Counts the number of executed indirect near branch

instructions that are not calls.

88H

07H

BR_INST_EXEC.NON_CALLS

Counts all non-call near branch instructions

executed, but not necessarily retired.

88H

08H

BR_INST_EXEC.RETURN_NEA

R

Counts indirect near branches that have a return

mnemonic.

88H

10H

BR_INST_EXEC.DIRECT_NEAR

_CALL

Counts unconditional near call branch instructions,

excluding non-call branch, executed.

88H

20H

BR_INST_EXEC.INDIRECT_NEA

R_CALL

Counts indirect near calls, including both register

and memory indirect, executed.

Table 19-19. Non-Architectural Performance Events In the Processor Core for

Processors Based on Intel® Microarchitecture Code Name Westmere (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment