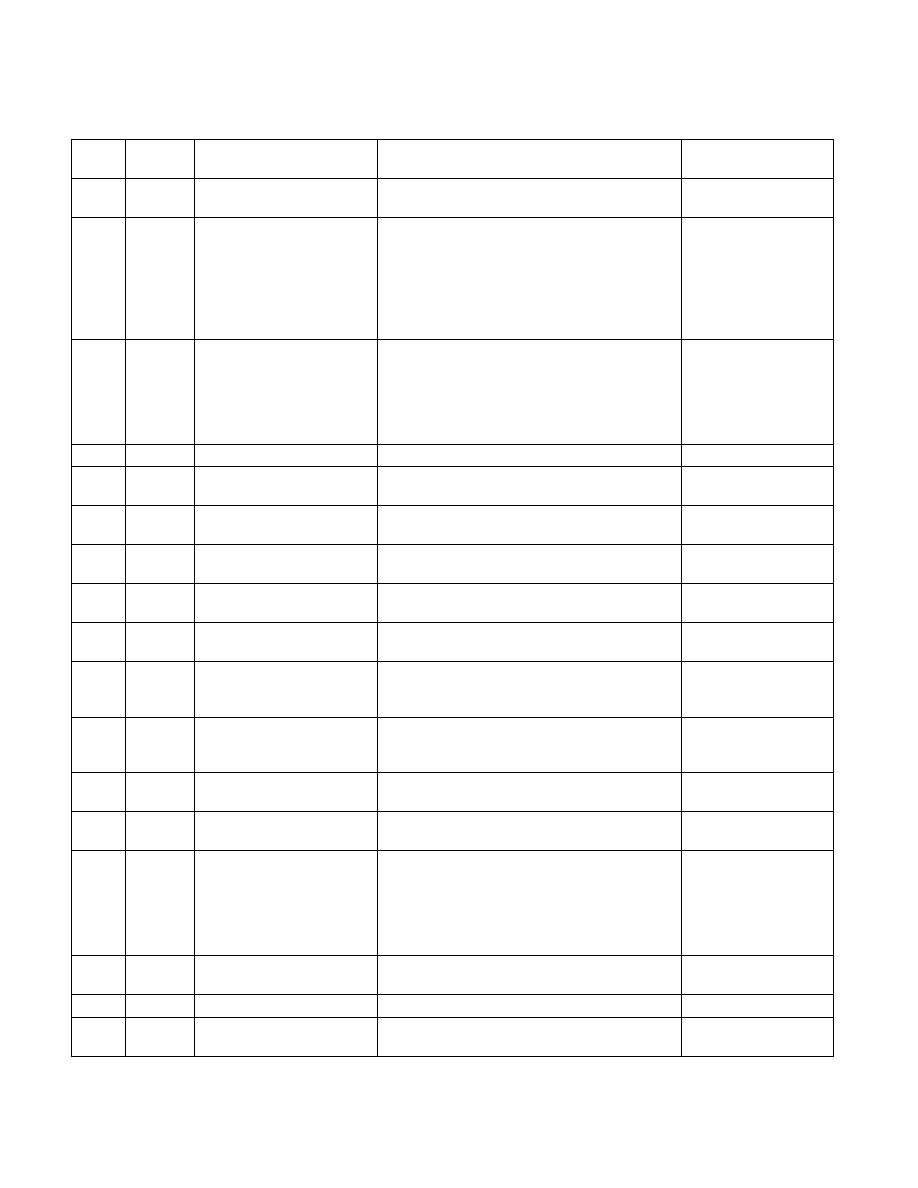

19-92 Vol. 3B

PERFORMANCE-MONITORING EVENTS

4EH

01H

L1D_PREFETCH.REQUESTS

Counts number of hardware prefetch requests

dispatched out of the prefetch FIFO.

Counter 0, 1 only.

4EH

02H

L1D_PREFETCH.MISS

Counts number of hardware prefetch requests that

miss the L1D. There are two prefetchers in the L1D.

A streamer, which predicts lines sequentially after

this one should be fetched, and the IP prefetcher

that remembers access patterns for the current

instruction. The streamer prefetcher stops on an

L1D hit, while the IP prefetcher does not.

Counter 0, 1 only.

4EH

04H

L1D_PREFETCH.TRIGGERS

Counts number of prefetch requests triggered by

the Finite State Machine and pushed into the

prefetch FIFO. Some of the prefetch requests are

dropped due to overwrites or competition between

the IP index prefetcher and streamer prefetcher.

The prefetch FIFO contains 4 entries.

Counter 0, 1 only.

4FH

10H

EPT.WALK_CYCLES

Counts Extended Page walk cycles.

51H

01H

L1D.REPL

Counts the number of lines brought into the L1 data

cache.

Counter 0, 1 only.

51H

02H

L1D.M_REPL

Counts the number of modified lines brought into

the L1 data cache.

Counter 0, 1 only.

51H

04H

L1D.M_EVICT

Counts the number of modified lines evicted from

the L1 data cache due to replacement.

Counter 0, 1 only.

51H

08H

L1D.M_SNOOP_EVICT

Counts the number of modified lines evicted from

the L1 data cache due to snoop HITM intervention.

Counter 0, 1 only.

52H

01H

L1D_CACHE_PREFETCH_LOCK

_FB_HIT

Counts the number of cacheable load lock

speculated instructions accepted into the fill buffer.

60H

01H

OFFCORE_REQUESTS_OUTST

ANDING.DEMAND.READ_DATA

Counts weighted cycles of offcore demand data

read requests. Does not include L2 prefetch

requests.

Counter 0.

60H

02H

OFFCORE_REQUESTS_OUTST

ANDING.DEMAND.READ_CODE

Counts weighted cycles of offcore demand code

read requests. Does not include L2 prefetch

requests.

Counter 0.

60H

04H

OFFCORE_REQUESTS_OUTST

ANDING.DEMAND.RFO

Counts weighted cycles of offcore demand RFO

requests. Does not include L2 prefetch requests.

Counter 0.

60H

08H

OFFCORE_REQUESTS_OUTST

ANDING.ANY.READ

Counts weighted cycles of offcore read requests of

any kind. Include L2 prefetch requests.

Counter 0.

63H

01H

CACHE_LOCK_CYCLES.L1D_L2 Cycle count during which the L1D and L2 are locked.

A lock is asserted when there is a locked memory

access, due to uncacheable memory, a locked

operation that spans two cache lines, or a page walk

from an uncacheable page table. This event does

not cause locks, it merely detects them.

Counter 0, 1 only. L1D

and L2 locks have a very

high performance

penalty and it is highly

recommended to avoid

such accesses.

63H

02H

CACHE_LOCK_CYCLES.L1D

Counts the number of cycles that cacheline in the

L1 data cache unit is locked.

Counter 0, 1 only.

6CH

01H

IO_TRANSACTIONS

Counts the number of completed I/O transactions.

80H

01H

L1I.HITS

Counts all instruction fetches that hit the L1

instruction cache.

Table 19-19. Non-Architectural Performance Events In the Processor Core for

Processors Based on Intel® Microarchitecture Code Name Westmere (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment