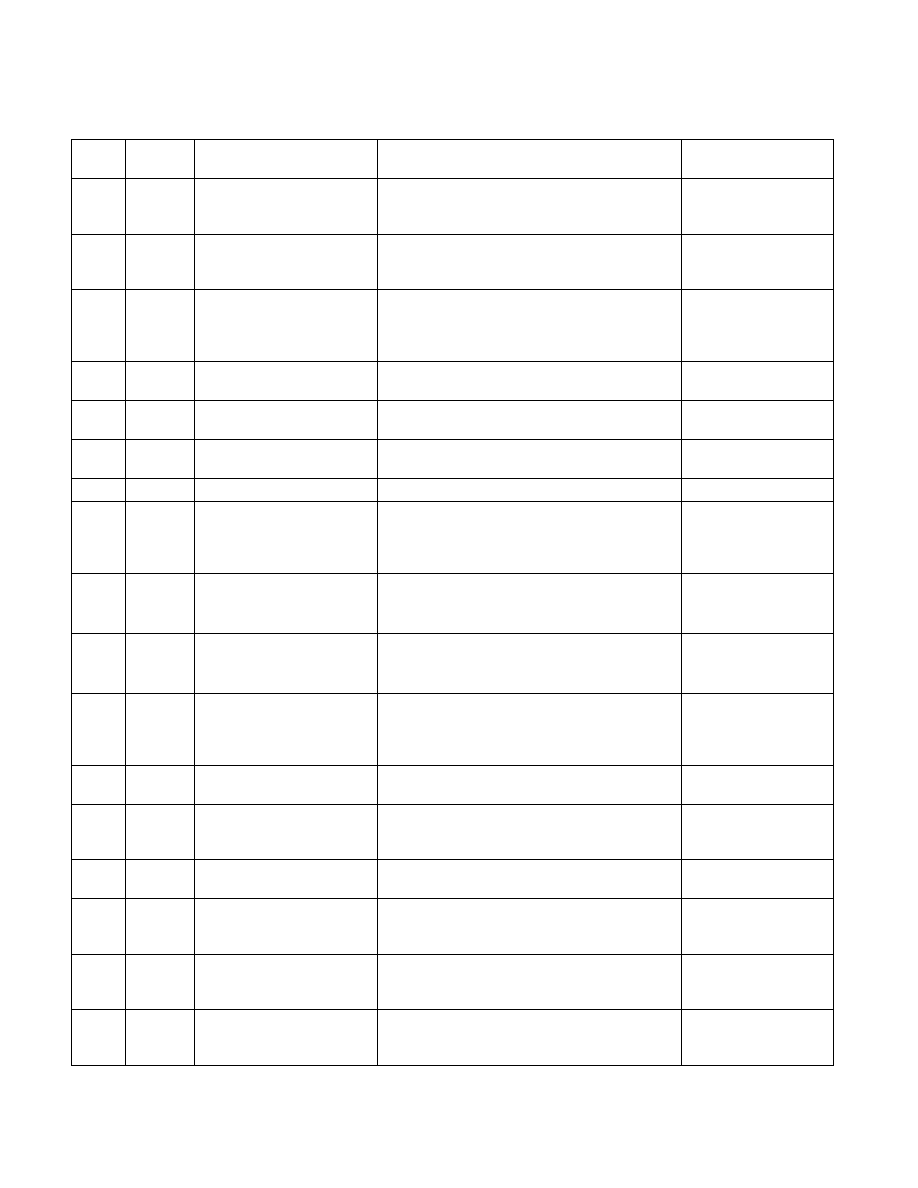

19-90 Vol. 3B

PERFORMANCE-MONITORING EVENTS

26H

0FH

L2_DATA_RQSTS.DEMAND.ME

SI

Counts all L2 data demand requests. L2 demand

loads are both L1D demand misses and L1D

prefetches.

26H

10H

L2_DATA_RQSTS.PREFETCH.I_

STATE

Counts number of L2 prefetch data loads where the

cache line to be loaded is in the I (invalid) state, i.e., a

cache miss.

26H

20H

L2_DATA_RQSTS.PREFETCH.S

_STATE

Counts number of L2 prefetch data loads where the

cache line to be loaded is in the S (shared) state. A

prefetch RFO will miss on an S state line, while a

prefetch read will hit on an S state line.

26H

40H

L2_DATA_RQSTS.PREFETCH.E

_STATE

Counts number of L2 prefetch data loads where the

cache line to be loaded is in the E (exclusive) state.

26H

80H

L2_DATA_RQSTS.PREFETCH.M

_STATE

Counts number of L2 prefetch data loads where the

cache line to be loaded is in the M (modified) state.

26H

F0H

L2_DATA_RQSTS.PREFETCH.M

ESI

Counts all L2 prefetch requests.

26H

FFH

L2_DATA_RQSTS.ANY

Counts all L2 data requests.

27H

01H

L2_WRITE.RFO.I_STATE

Counts number of L2 demand store RFO requests

where the cache line to be loaded is in the I (invalid)

state, i.e., a cache miss. The L1D prefetcher does

not issue a RFO prefetch.

This is a demand RFO

request.

27H

02H

L2_WRITE.RFO.S_STATE

Counts number of L2 store RFO requests where the

cache line to be loaded is in the S (shared) state.

The L1D prefetcher does not issue a RFO prefetch.

This is a demand RFO

request.

27H

08H

L2_WRITE.RFO.M_STATE

Counts number of L2 store RFO requests where the

cache line to be loaded is in the M (modified) state.

The L1D prefetcher does not issue a RFO prefetch.

This is a demand RFO

request.

27H

0EH

L2_WRITE.RFO.HIT

Counts number of L2 store RFO requests where the

cache line to be loaded is in either the S, E or M

states. The L1D prefetcher does not issue a RFO

prefetch.

This is a demand RFO

request.

27H

0FH

L2_WRITE.RFO.MESI

Counts all L2 store RFO requests. The L1D

prefetcher does not issue a RFO prefetch.

This is a demand RFO

request.

27H

10H

L2_WRITE.LOCK.I_STATE

Counts number of L2 demand lock RFO requests

where the cache line to be loaded is in the I (invalid)

state, i.e., a cache miss.

27H

20H

L2_WRITE.LOCK.S_STATE

Counts number of L2 lock RFO requests where the

cache line to be loaded is in the S (shared) state.

27H

40H

L2_WRITE.LOCK.E_STATE

Counts number of L2 demand lock RFO requests

where the cache line to be loaded is in the E

(exclusive) state.

27H

80H

L2_WRITE.LOCK.M_STATE

Counts number of L2 demand lock RFO requests

where the cache line to be loaded is in the M

(modified) state.

27H

E0H

L2_WRITE.LOCK.HIT

Counts number of L2 demand lock RFO requests

where the cache line to be loaded is in either the S,

E, or M state.

Table 19-19. Non-Architectural Performance Events In the Processor Core for

Processors Based on Intel® Microarchitecture Code Name Westmere (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment