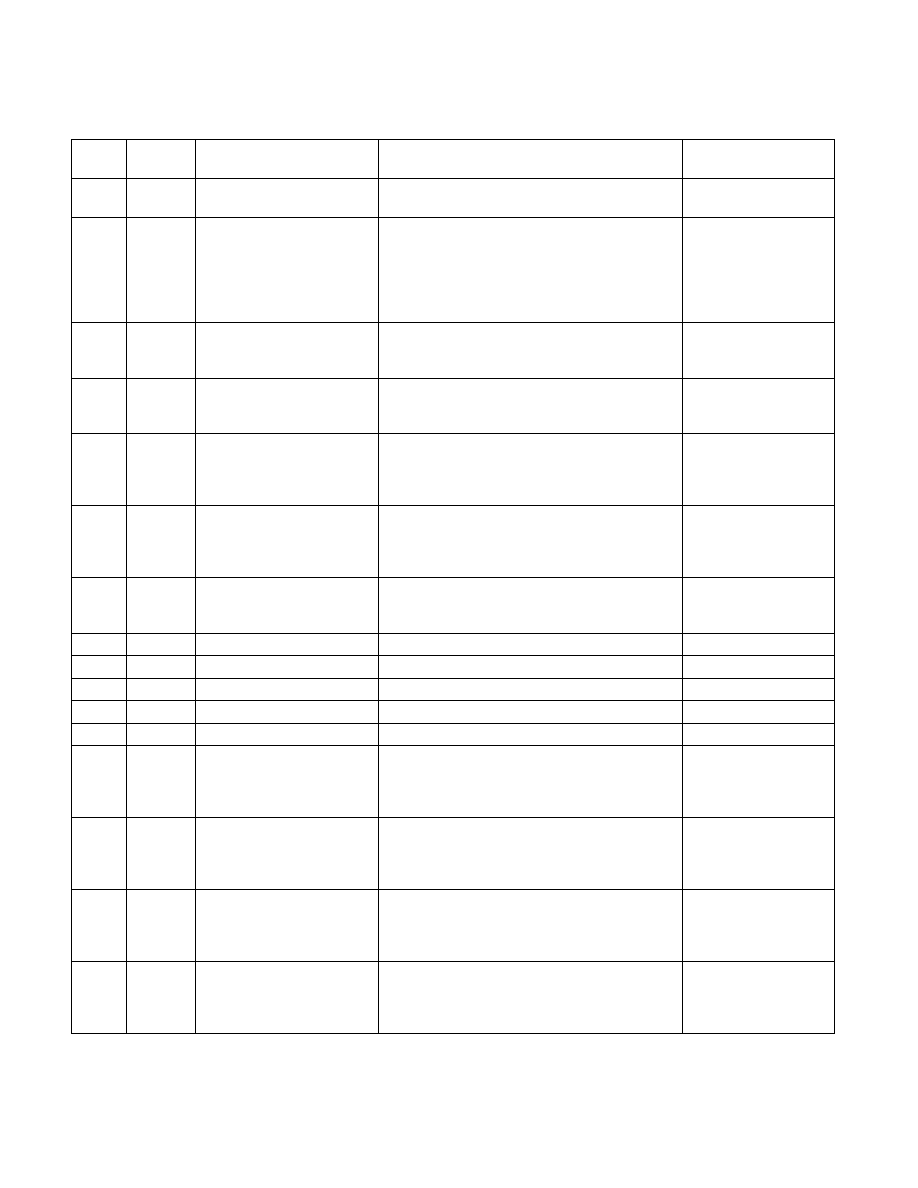

Vol. 3B 19-89

PERFORMANCE-MONITORING EVENTS

24H

03H

L2_RQSTS.LOADS

Counts all L2 load requests. L2 loads include both

L1D demand misses as well as L1D prefetches.

24H

04H

L2_RQSTS.RFO_HIT

Counts the number of store RFO requests that hit

the L2 cache. L2 RFO requests include both L1D

demand RFO misses as well as L1D RFO prefetches.

Count includes WC memory requests, where the

data is not fetched but the permission to write the

line is required.

24H

08H

L2_RQSTS.RFO_MISS

Counts the number of store RFO requests that miss

the L2 cache. L2 RFO requests include both L1D

demand RFO misses as well as L1D RFO prefetches.

24H

0CH

L2_RQSTS.RFOS

Counts all L2 store RFO requests. L2 RFO requests

include both L1D demand RFO misses as well as L1D

RFO prefetches.

24H

10H

L2_RQSTS.IFETCH_HIT

Counts number of instruction fetches that hit the

L2 cache. L2 instruction fetches include both L1I

demand misses as well as L1I instruction

prefetches.

24H

20H

L2_RQSTS.IFETCH_MISS

Counts number of instruction fetches that miss the

L2 cache. L2 instruction fetches include both L1I

demand misses as well as L1I instruction

prefetches.

24H

30H

L2_RQSTS.IFETCHES

Counts all instruction fetches. L2 instruction fetches

include both L1I demand misses as well as L1I

instruction prefetches.

24H

40H

L2_RQSTS.PREFETCH_HIT

Counts L2 prefetch hits for both code and data.

24H

80H

L2_RQSTS.PREFETCH_MISS

Counts L2 prefetch misses for both code and data.

24H

C0H

L2_RQSTS.PREFETCHES

Counts all L2 prefetches for both code and data.

24H

AAH

L2_RQSTS.MISS

Counts all L2 misses for both code and data.

24H

FFH

L2_RQSTS.REFERENCES

Counts all L2 requests for both code and data.

26H

01H

L2_DATA_RQSTS.DEMAND.I_S

TATE

Counts number of L2 data demand loads where the

cache line to be loaded is in the I (invalid) state, i.e., a

cache miss. L2 demand loads are both L1D demand

misses and L1D prefetches.

26H

02H

L2_DATA_RQSTS.DEMAND.S_

STATE

Counts number of L2 data demand loads where the

cache line to be loaded is in the S (shared) state. L2

demand loads are both L1D demand misses and L1D

prefetches.

26H

04H

L2_DATA_RQSTS.DEMAND.E_

STATE

Counts number of L2 data demand loads where the

cache line to be loaded is in the E (exclusive) state.

L2 demand loads are both L1D demand misses and

L1D prefetches.

26H

08H

L2_DATA_RQSTS.DEMAND.M_

STATE

Counts number of L2 data demand loads where the

cache line to be loaded is in the M (modified) state.

L2 demand loads are both L1D demand misses and

L1D prefetches.

Table 19-19. Non-Architectural Performance Events In the Processor Core for

Processors Based on Intel® Microarchitecture Code Name Westmere (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment