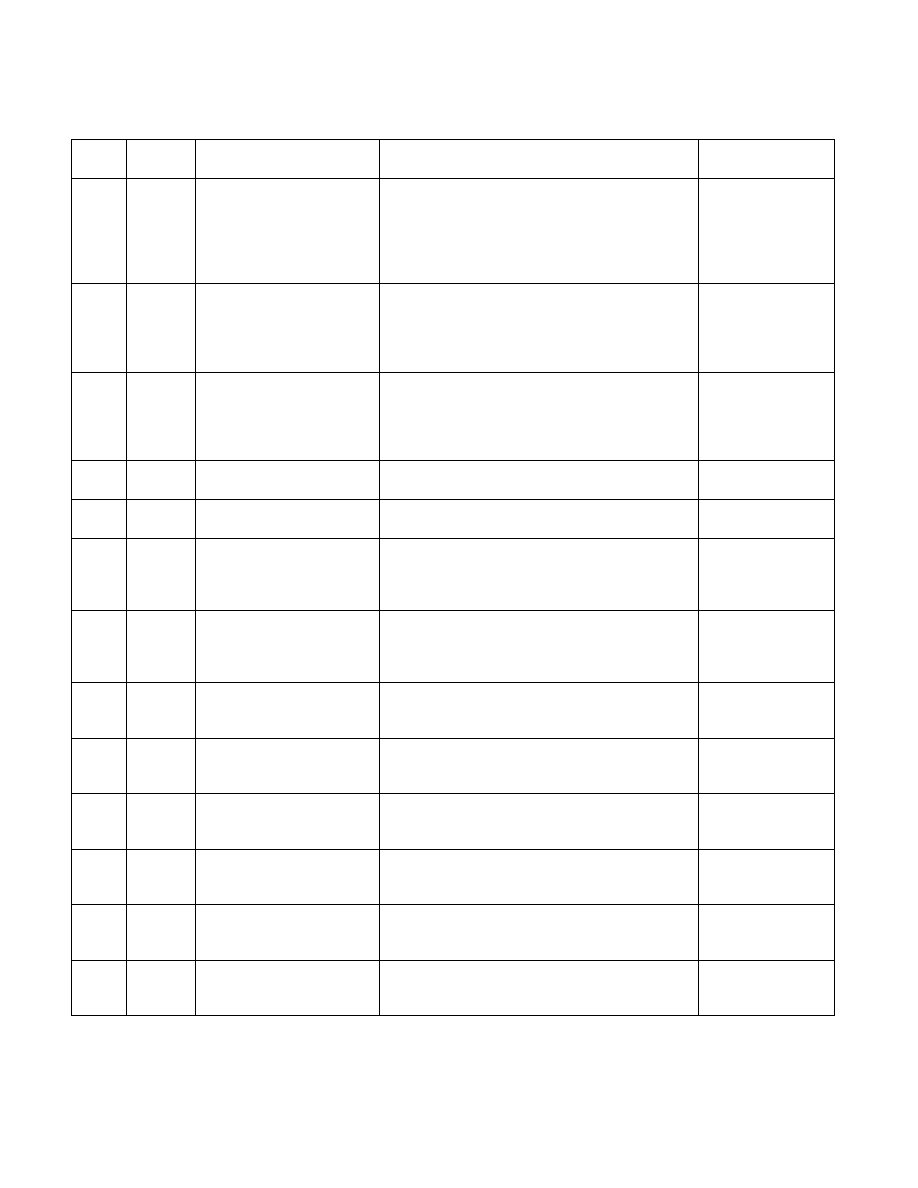

Vol. 3B 19-83

PERFORMANCE-MONITORING EVENTS

41H

20H

UNC_QPI_TX_STALLED_MULTI

_FLIT.NCS.LINK_1

Counts cycles the Quickpath outbound link 1 Non-

Coherent Standard virtual channel is stalled due to lack

of VNA and VN0 credits. Note that this event does not

filter out when a flit would not have been selected for

arbitration because another virtual channel is getting

arbitrated.

41H

07H

UNC_QPI_TX_STALLED_MULTI

_FLIT.LINK_0

Counts cycles the Quickpath outbound link 0 virtual

channels are stalled due to lack of VNA and VN0

credits. Note that this event does not filter out when a

flit would not have been selected for arbitration

because another virtual channel is getting arbitrated.

41H

38H

UNC_QPI_TX_STALLED_MULTI

_FLIT.LINK_1

Counts cycles the Quickpath outbound link 1 virtual

channels are stalled due to lack of VNA and VN0

credits. Note that this event does not filter out when a

flit would not have been selected for arbitration

because another virtual channel is getting arbitrated.

42H

02H

UNC_QPI_TX_HEADER.BUSY.LI

NK_0

Number of cycles that the header buffer in the

Quickpath Interface outbound link 0 is busy.

42H

08H

UNC_QPI_TX_HEADER.BUSY.LI

NK_1

Number of cycles that the header buffer in the

Quickpath Interface outbound link 1 is busy.

43H

01H

UNC_QPI_RX_NO_PPT_CREDI

T.STALLS.LINK_0

Number of cycles that snoop packets incoming to the

Quickpath Interface link 0 are stalled and not sent to

the GQ because the GQ Peer Probe Tracker (PPT) does

not have any available entries.

43H

02H

UNC_QPI_RX_NO_PPT_CREDI

T.STALLS.LINK_1

Number of cycles that snoop packets incoming to the

Quickpath Interface link 1 are stalled and not sent to

the GQ because the GQ Peer Probe Tracker (PPT) does

not have any available entries.

60H

01H

UNC_DRAM_OPEN.CH0

Counts number of DRAM Channel 0 open commands

issued either for read or write. To read or write data,

the referenced DRAM page must first be opened.

60H

02H

UNC_DRAM_OPEN.CH1

Counts number of DRAM Channel 1 open commands

issued either for read or write. To read or write data,

the referenced DRAM page must first be opened.

60H

04H

UNC_DRAM_OPEN.CH2

Counts number of DRAM Channel 2 open commands

issued either for read or write. To read or write data,

the referenced DRAM page must first be opened.

61H

01H

UNC_DRAM_PAGE_CLOSE.CH0 DRAM channel 0 command issued to CLOSE a page due

to page idle timer expiration. Closing a page is done by

issuing a precharge.

61H

02H

UNC_DRAM_PAGE_CLOSE.CH1 DRAM channel 1 command issued to CLOSE a page due

to page idle timer expiration. Closing a page is done by

issuing a precharge.

61H

04H

UNC_DRAM_PAGE_CLOSE.CH2 DRAM channel 2 command issued to CLOSE a page due

to page idle timer expiration. Closing a page is done by

issuing a precharge.

Table 19-18. Non-Architectural Performance Events In the Processor Uncore for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment