19-78 Vol. 3B

PERFORMANCE-MONITORING EVENTS

24H

02H

UNC_QHL_ADDRESS_CONFLIC

TS.2WAY

Counts number of QHL Active Address Table (AAT)

entries that saw a max of 2 conflicts. The AAT is a

structure that tracks requests that are in conflict. The

requests themselves are in the home tracker entries.

The count is reported when an AAT entry deallocates.

24H

04H

UNC_QHL_ADDRESS_CONFLIC

TS.3WAY

Counts number of QHL Active Address Table (AAT)

entries that saw a max of 3 conflicts. The AAT is a

structure that tracks requests that are in conflict. The

requests themselves are in the home tracker entries.

The count is reported when an AAT entry deallocates.

25H

01H

UNC_QHL_CONFLICT_CYCLES.I

OH

Counts cycles the Quickpath Home Logic IOH Tracker

contains two or more requests with an address

conflict. A max of 3 requests can be in conflict.

25H

02H

UNC_QHL_CONFLICT_CYCLES.

REMOTE

Counts cycles the Quickpath Home Logic Remote

Tracker contains two or more requests with an

address conflict. A max of 3 requests can be in conflict.

25H

04H

UNC_QHL_CONFLICT_CYCLES.

LOCAL

Counts cycles the Quickpath Home Logic Local Tracker

contains two or more requests with an address

conflict. A max of 3 requests can be in conflict.

26H

01H

UNC_QHL_TO_QMC_BYPASS

Counts number or requests to the Quickpath Memory

Controller that bypass the Quickpath Home Logic. All

local accesses can be bypassed. For remote requests,

only read requests can be bypassed.

27H

01H

UNC_QMC_NORMAL_FULL.RE

AD.CH0

Uncore cycles all the entries in the DRAM channel 0

medium or low priority queue are occupied with read

requests.

27H

02H

UNC_QMC_NORMAL_FULL.RE

AD.CH1

Uncore cycles all the entries in the DRAM channel 1

medium or low priority queue are occupied with read

requests.

27H

04H

UNC_QMC_NORMAL_FULL.RE

AD.CH2

Uncore cycles all the entries in the DRAM channel 2

medium or low priority queue are occupied with read

requests.

27H

08H

UNC_QMC_NORMAL_FULL.WRI

TE.CH0

Uncore cycles all the entries in the DRAM channel 0

medium or low priority queue are occupied with write

requests.

27H

10H

UNC_QMC_NORMAL_FULL.WRI

TE.CH1

Counts cycles all the entries in the DRAM channel 1

medium or low priority queue are occupied with write

requests.

27H

20H

UNC_QMC_NORMAL_FULL.WRI

TE.CH2

Uncore cycles all the entries in the DRAM channel 2

medium or low priority queue are occupied with write

requests.

28H

01H

UNC_QMC_ISOC_FULL.READ.C

H0

Counts cycles all the entries in the DRAM channel 0

high priority queue are occupied with isochronous

read requests.

28H

02H

UNC_QMC_ISOC_FULL.READ.C

H1

Counts cycles all the entries in the DRAM channel

1high priority queue are occupied with isochronous

read requests.

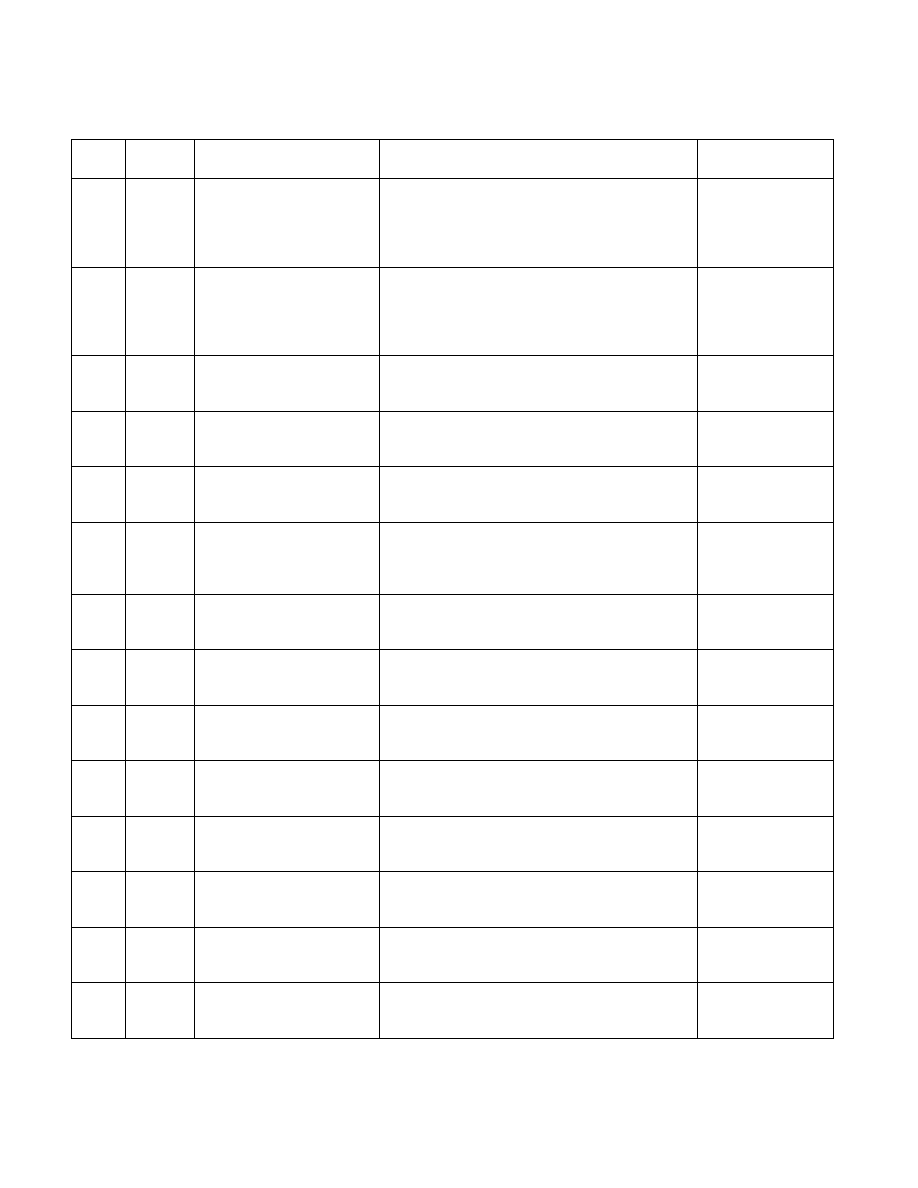

Table 19-18. Non-Architectural Performance Events In the Processor Uncore for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment