19-72 Vol. 3B

PERFORMANCE-MONITORING EVENTS

DBH

01H

UOP_UNFUSION

Counts unfusion events due to floating-point

exception to a fused uop.

E0H

01H

BR_INST_DECODED

Counts the number of branch instructions decoded.

E5H

01H

BPU_MISSED_CALL_RET

Counts number of times the Branch Prediction Unit

missed predicting a call or return branch.

E6H

01H

BACLEAR.CLEAR

Counts the number of times the front end is

resteered, mainly when the Branch Prediction Unit

cannot provide a correct prediction and this is

corrected by the Branch Address Calculator at the

front end. This can occur if the code has many

branches such that they cannot be consumed by

the BPU. Each BACLEAR asserted by the BAC

generates approximately an 8 cycle bubble in the

instruction fetch pipeline. The effect on total

execution time depends on the surrounding code.

E6H

02H

BACLEAR.BAD_TARGET

Counts number of Branch Address Calculator clears

(BACLEAR) asserted due to conditional branch

instructions in which there was a target hit but the

direction was wrong. Each BACLEAR asserted by

the BAC generates approximately an 8 cycle bubble

in the instruction fetch pipeline.

E8H

01H

BPU_CLEARS.EARLY

Counts early (normal) Branch Prediction Unit clears:

BPU predicted a taken branch after incorrectly

assuming that it was not taken.

The BPU clear leads to 2

cycle bubble in the front

end.

E8H

02H

BPU_CLEARS.LATE

Counts late Branch Prediction Unit clears due to

Most Recently Used conflicts. The PBU clear leads

to a 3 cycle bubble in the front end.

F0H

01H

L2_TRANSACTIONS.LOAD

Counts L2 load operations due to HW prefetch or

demand loads.

F0H

02H

L2_TRANSACTIONS.RFO

Counts L2 RFO operations due to HW prefetch or

demand RFOs.

F0H

04H

L2_TRANSACTIONS.IFETCH

Counts L2 instruction fetch operations due to HW

prefetch or demand ifetch.

F0H

08H

L2_TRANSACTIONS.PREFETCH Counts L2 prefetch operations.

F0H

10H

L2_TRANSACTIONS.L1D_WB

Counts L1D writeback operations to the L2.

F0H

20H

L2_TRANSACTIONS.FILL

Counts L2 cache line fill operations due to load, RFO,

L1D writeback or prefetch.

F0H

40H

L2_TRANSACTIONS.WB

Counts L2 writeback operations to the L3.

F0H

80H

L2_TRANSACTIONS.ANY

Counts all L2 cache operations.

F1H

02H

L2_LINES_IN.S_STATE

Counts the number of cache lines allocated in the

L2 cache in the S (shared) state.

F1H

04H

L2_LINES_IN.E_STATE

Counts the number of cache lines allocated in the

L2 cache in the E (exclusive) state.

F1H

07H

L2_LINES_IN.ANY

Counts the number of cache lines allocated in the

L2 cache.

F2H

01H

L2_LINES_OUT.DEMAND_CLEA

N

Counts L2 clean cache lines evicted by a demand

request.

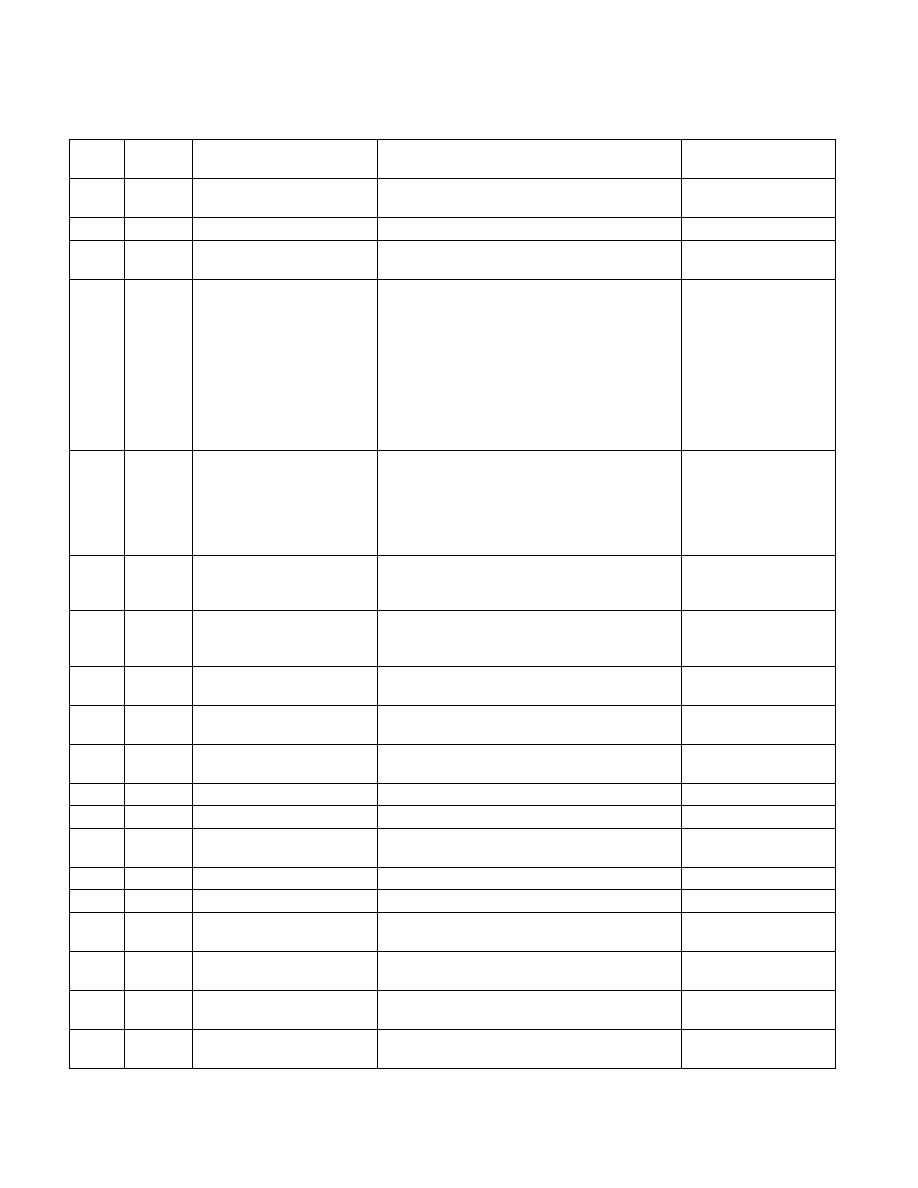

Table 19-17. Non-Architectural Performance Events In the Processor Core for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment