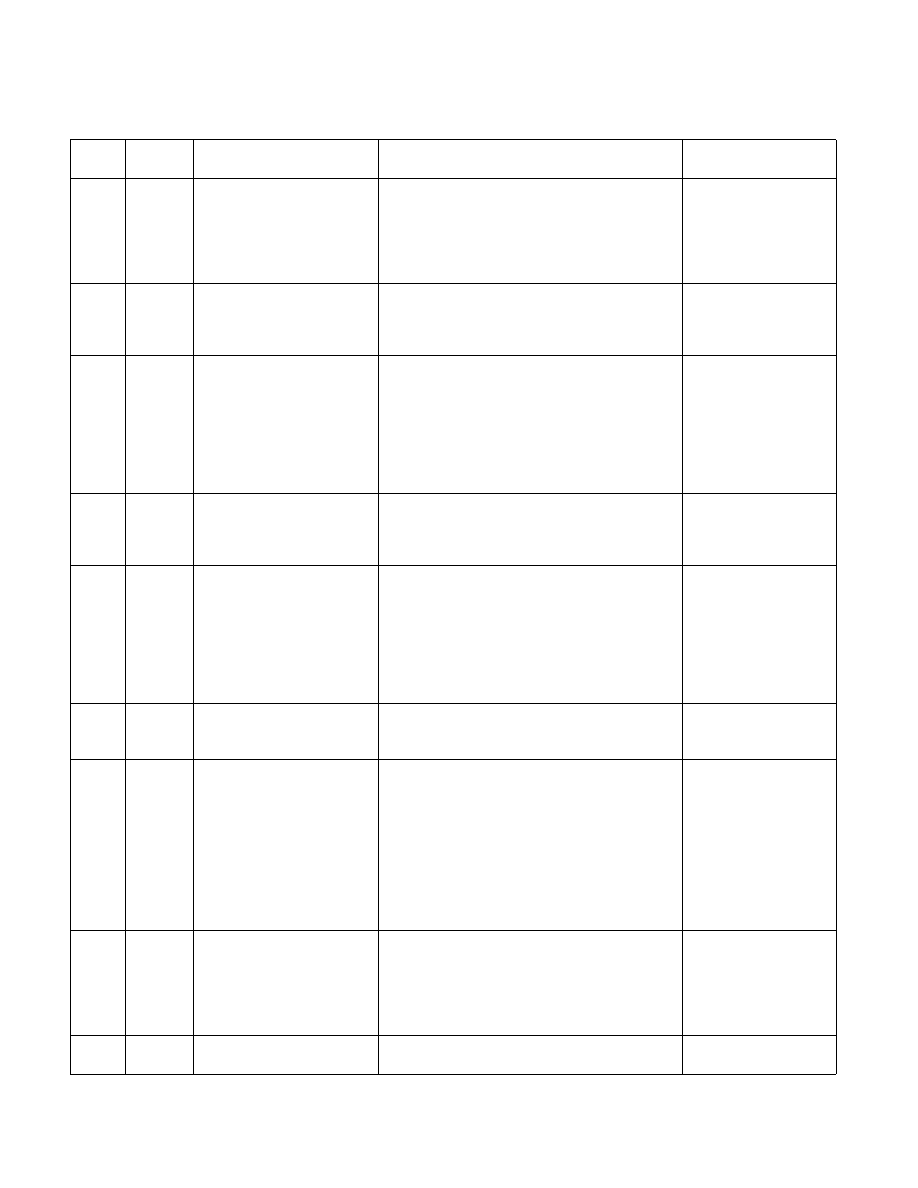

Vol. 3B 19-71

PERFORMANCE-MONITORING EVENTS

D1H

04H

UOPS_DECODED.ESP_FOLDING Counts number of stack pointer (ESP) instructions

decoded: push, pop, call, ret, etc. ESP instructions do

not generate a Uop to increment or decrement ESP.

Instead, they update an ESP_Offset register that

keeps track of the delta to the current value of the

ESP register.

D1H

08H

UOPS_DECODED.ESP_SYNC

Counts number of stack pointer (ESP) sync

operations where an ESP instruction is corrected by

adding the ESP offset register to the current value

of the ESP register.

D2H

01H

RAT_STALLS.FLAGS

Counts the number of cycles during which

execution stalled due to several reasons, one of

which is a partial flag register stall. A partial register

stall may occur when two conditions are met: 1) an

instruction modifies some, but not all, of the flags in

the flag register and 2) the next instruction, which

depends on flags, depends on flags that were not

modified by this instruction.

D2H

02H

RAT_STALLS.REGISTERS

This event counts the number of cycles instruction

execution latency became longer than the defined

latency because the instruction used a register that

was partially written by previous instruction.

D2H

04H

RAT_STALLS.ROB_READ_POR

T

Counts the number of cycles when ROB read port

stalls occurred, which did not allow new micro-ops

to enter the out-of-order pipeline. Note that, at this

stage in the pipeline, additional stalls may occur at

the same cycle and prevent the stalled micro-ops

from entering the pipe. In such a case, micro-ops

retry entering the execution pipe in the next cycle

and the ROB-read port stall is counted again.

D2H

08H

RAT_STALLS.SCOREBOARD

Counts the cycles where we stall due to

microarchitecturally required serialization.

Microcode scoreboarding stalls.

D2H

0FH

RAT_STALLS.ANY

Counts all Register Allocation Table stall cycles due

to: Cycles when ROB read port stalls occurred,

which did not allow new micro-ops to enter the

execution pipe. Cycles when partial register stalls

occurred. Cycles when flag stalls occurred. Cycles

floating-point unit (FPU) status word stalls occurred.

To count each of these conditions separately use

the events: RAT_STALLS.ROB_READ_PORT,

RAT_STALLS.PARTIAL, RAT_STALLS.FLAGS, and

RAT_STALLS.FPSW.

D4H

01H

SEG_RENAME_STALLS

Counts the number of stall cycles due to the lack of

renaming resources for the ES, DS, FS, and GS

segment registers. If a segment is renamed but not

retired and a second update to the same segment

occurs, a stall occurs in the front end of the pipeline

until the renamed segment retires.

D5H

01H

ES_REG_RENAMES

Counts the number of times the ES segment

register is renamed.

Table 19-17. Non-Architectural Performance Events In the Processor Core for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment