19-70 Vol. 3B

PERFORMANCE-MONITORING EVENTS

C7H

08H

SSEX_UOPS_RETIRED.SCALAR

_DOUBLE

Counts SIMD scalar double-precision floating point

Uops retired.

C7H

10H

SSEX_UOPS_RETIRED.VECTOR

_INTEGER

Counts 128-bit SIMD vector integer Uops retired.

C8H

20H

ITLB_MISS_RETIRED

Counts the number of retired instructions that

missed the ITLB when the instruction was fetched.

CBH

01H

MEM_LOAD_RETIRED.L1D_HIT Counts number of retired loads that hit the L1 data

cache.

CBH

02H

MEM_LOAD_RETIRED.L2_HIT

Counts number of retired loads that hit the L2 data

cache.

CBH

04H

MEM_LOAD_RETIRED.L3_UNS

HARED_HIT

Counts number of retired loads that hit their own,

unshared lines in the L3 cache.

CBH

08H

MEM_LOAD_RETIRED.OTHER_

CORE_L2_HIT_HITM

Counts number of retired loads that hit in a sibling

core's L2 (on die core). Since the L3 is inclusive of all

cores on the package, this is an L3 hit. This counts

both clean and modified hits.

CBH

10H

MEM_LOAD_RETIRED.L3_MISS Counts number of retired loads that miss the L3

cache. The load was satisfied by a remote socket,

local memory or an IOH.

CBH

40H

MEM_LOAD_RETIRED.HIT_LFB Counts number of retired loads that miss the L1D

and the address is located in an allocated line fill

buffer and will soon be committed to cache. This is

counting secondary L1D misses.

CBH

80H

MEM_LOAD_RETIRED.DTLB_MI

SS

Counts the number of retired loads that missed the

DTLB. The DTLB miss is not counted if the load

operation causes a fault. This event counts loads

from cacheable memory only. The event does not

count loads by software prefetches. Counts both

primary and secondary misses to the TLB.

CCH

01H

FP_MMX_TRANS.TO_FP

Counts the first floating-point instruction following

any MMX instruction. You can use this event to

estimate the penalties for the transitions between

floating-point and MMX technology states.

CCH

02H

FP_MMX_TRANS.TO_MMX

Counts the first MMX instruction following a

floating-point instruction. You can use this event to

estimate the penalties for the transitions between

floating-point and MMX technology states.

CCH

03H

FP_MMX_TRANS.ANY

Counts all transitions from floating point to MMX

instructions and from MMX instructions to floating

point instructions. You can use this event to

estimate the penalties for the transitions between

floating-point and MMX technology states.

D0H

01H

MACRO_INSTS.DECODED

Counts the number of instructions decoded, (but

not necessarily executed or retired).

D1H

02H

UOPS_DECODED.MS

Counts the number of Uops decoded by the

Microcode Sequencer, MS. The MS delivers uops

when the instruction is more than 4 uops long or a

microcode assist is occurring.

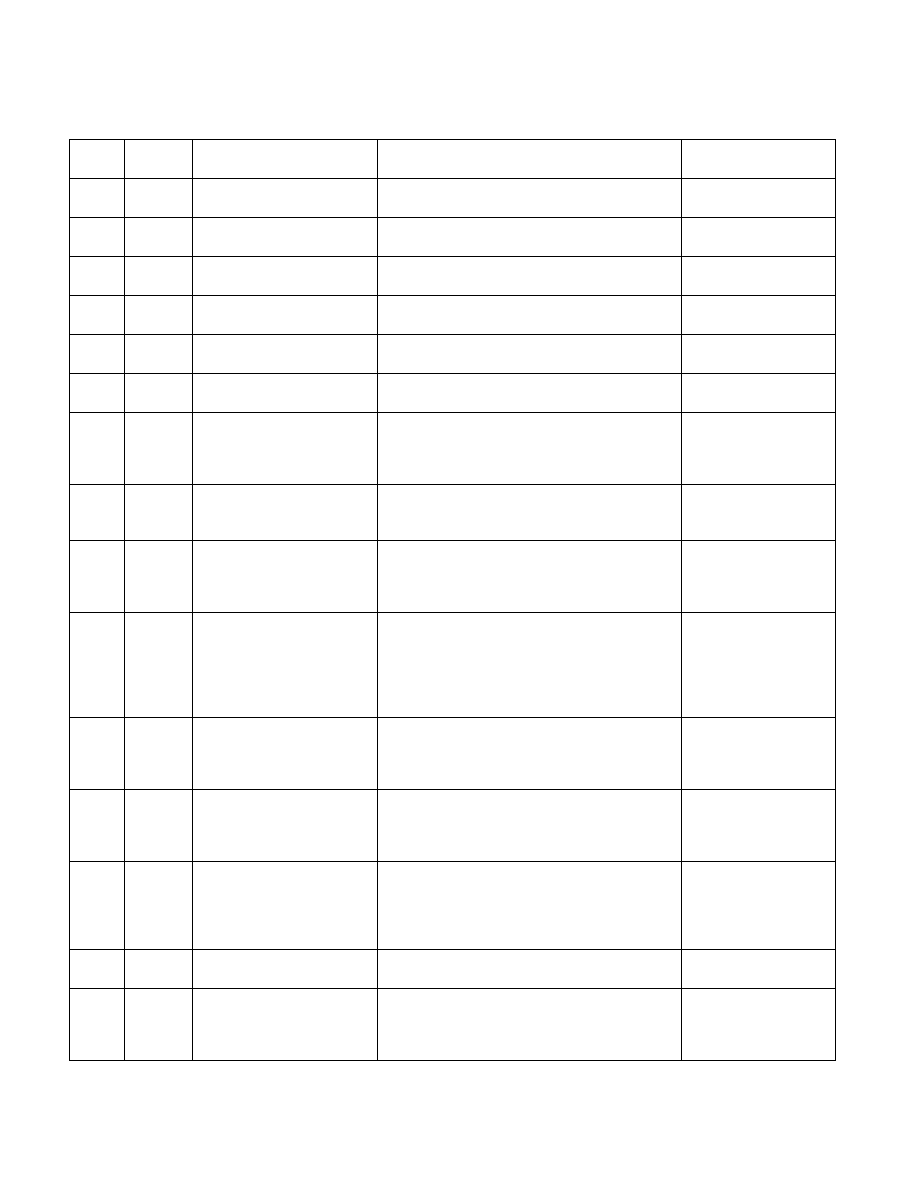

Table 19-17. Non-Architectural Performance Events In the Processor Core for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment