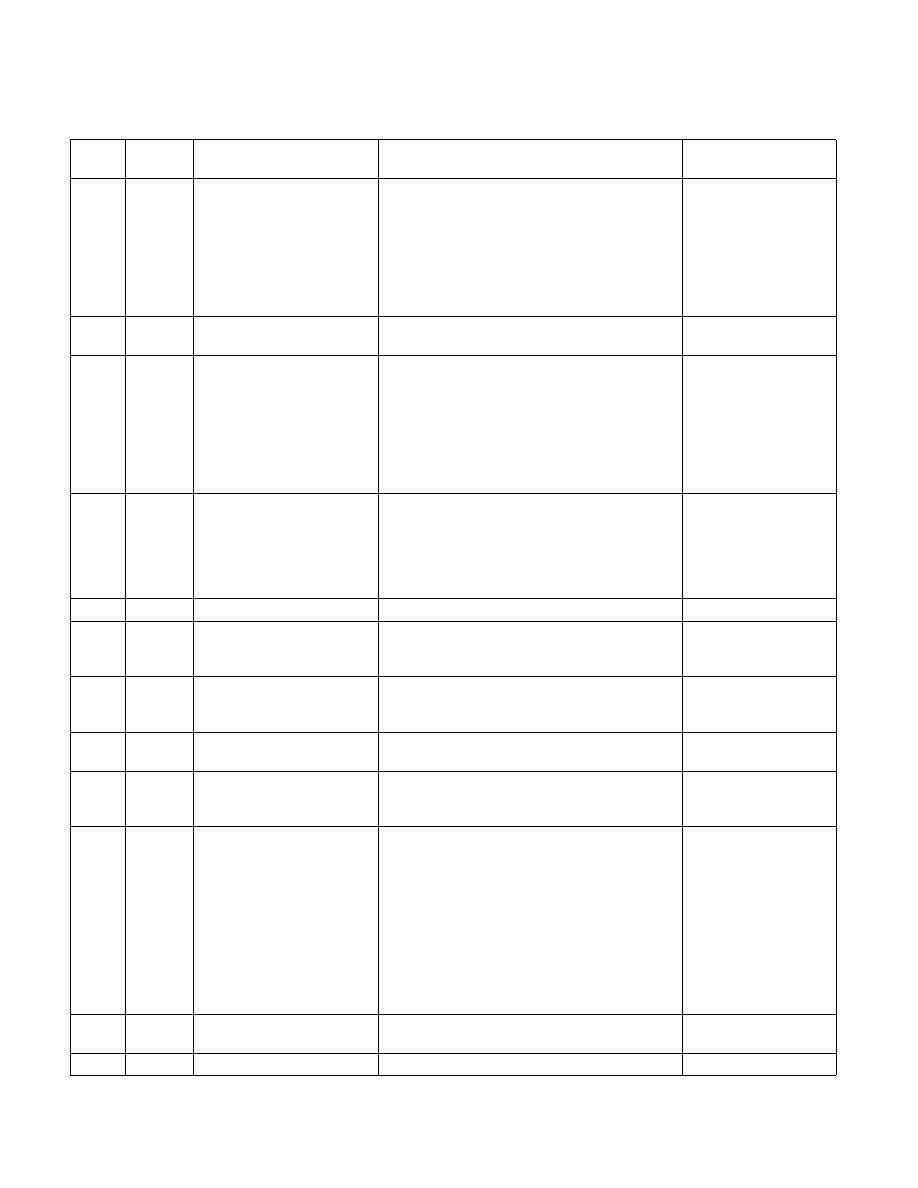

Vol. 3B 19-67

PERFORMANCE-MONITORING EVENTS

A2H

01H

RESOURCE_STALLS.ANY

Counts the number of Allocator resource related

stalls. Includes register renaming buffer entries,

memory buffer entries. In addition to resource

related stalls, this event counts some other events.

Includes stalls arising during branch misprediction

recovery, such as if retirement of the mispredicted

branch is delayed and stalls arising while store

buffer is draining from synchronizing operations.

Does not include stalls

due to SuperQ (off core)

queue full, too many

cache misses, etc.

A2H

02H

RESOURCE_STALLS.LOAD

Counts the cycles of stall due to lack of load buffer

for load operation.

A2H

04H

RESOURCE_STALLS.RS_FULL

This event counts the number of cycles when the

number of instructions in the pipeline waiting for

execution reaches the limit the processor can

handle. A high count of this event indicates that

there are long latency operations in the pipe

(possibly load and store operations that miss the L2

cache, or instructions dependent upon instructions

further down the pipeline that have yet to retire.

When RS is full, new

instructions cannot enter

the reservation station

and start execution.

A2H

08H

RESOURCE_STALLS.STORE

This event counts the number of cycles that a

resource related stall will occur due to the number

of store instructions reaching the limit of the

pipeline, (i.e. all store buffers are used). The stall

ends when a store instruction commits its data to

the cache or memory.

A2H

10H

RESOURCE_STALLS.ROB_FULL Counts the cycles of stall due to re-order buffer full.

A2H

20H

RESOURCE_STALLS.FPCW

Counts the number of cycles while execution was

stalled due to writing the floating-point unit (FPU)

control word.

A2H

40H

RESOURCE_STALLS.MXCSR

Stalls due to the MXCSR register rename occurring

to close to a previous MXCSR rename. The MXCSR

provides control and status for the MMX registers.

A2H

80H

RESOURCE_STALLS.OTHER

Counts the number of cycles while execution was

stalled due to other resource issues.

A6H

01H

MACRO_INSTS.FUSIONS_DECO

DED

Counts the number of instructions decoded that are

macro-fused but not necessarily executed or

retired.

A7H

01H

BACLEAR_FORCE_IQ

Counts number of times a BACLEAR was forced by

the Instruction Queue. The IQ is also responsible for

providing conditional branch prediction direction

based on a static scheme and dynamic data

provided by the L2 Branch Prediction Unit. If the

conditional branch target is not found in the Target

Array and the IQ predicts that the branch is taken,

then the IQ will force the Branch Address Calculator

to issue a BACLEAR. Each BACLEAR asserted by the

BAC generates approximately an 8 cycle bubble in

the instruction fetch pipeline.

A8H

01H

LSD.UOPS

Counts the number of micro-ops delivered by loop

stream detector.

Use cmask=1 and invert

to count cycles.

AEH

01H

ITLB_FLUSH

Counts the number of ITLB flushes.

Table 19-17. Non-Architectural Performance Events In the Processor Core for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment