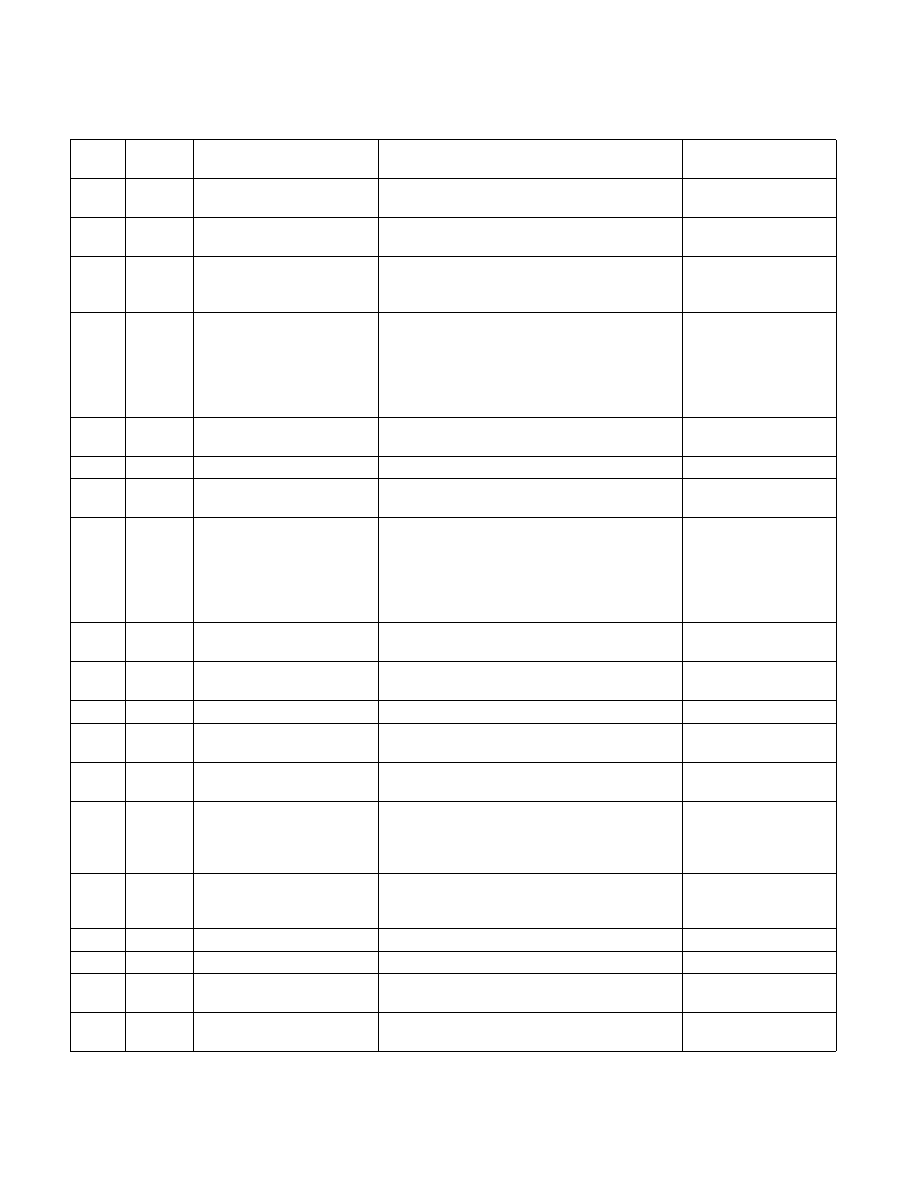

Vol. 3B 19-65

PERFORMANCE-MONITORING EVENTS

51H

08H

L1D.M_SNOOP_EVICT

Counts the number of modified lines evicted from

the L1 data cache due to snoop HITM intervention.

Counter 0, 1 only.

52H

01H

L1D_CACHE_PREFETCH_LOCK

_FB_HIT

Counts the number of cacheable load lock

speculated instructions accepted into the fill buffer.

53H

01H

L1D_CACHE_LOCK_FB_HIT

Counts the number of cacheable load lock

speculated or retired instructions accepted into the

fill buffer.

63H

01H

CACHE_LOCK_CYCLES.L1D_L2 Cycle count during which the L1D and L2 are locked.

A lock is asserted when there is a locked memory

access, due to uncacheable memory, a locked

operation that spans two cache lines, or a page walk

from an uncacheable page table.

Counter 0, 1 only. L1D

and L2 locks have a very

high performance

penalty and it is highly

recommended to avoid

such accesses.

63H

02H

CACHE_LOCK_CYCLES.L1D

Counts the number of cycles that cacheline in the

L1 data cache unit is locked.

Counter 0, 1 only.

6CH

01H

IO_TRANSACTIONS

Counts the number of completed I/O transactions.

80H

01H

L1I.HITS

Counts all instruction fetches that hit the L1

instruction cache.

80H

02H

L1I.MISSES

Counts all instruction fetches that miss the L1I

cache. This includes instruction cache misses,

streaming buffer misses, victim cache misses and

uncacheable fetches. An instruction fetch miss is

counted only once and not once for every cycle it is

outstanding.

80H

03H

L1I.READS

Counts all instruction fetches, including uncacheable

fetches that bypass the L1I.

80H

04H

L1I.CYCLES_STALLED

Cycle counts for which an instruction fetch stalls

due to a L1I cache miss, ITLB miss or ITLB fault.

82H

01H

LARGE_ITLB.HIT

Counts number of large ITLB hits.

85H

01H

ITLB_MISSES.ANY

Counts the number of misses in all levels of the ITLB

which causes a page walk.

85H

02H

ITLB_MISSES.WALK_COMPLET

ED

Counts number of misses in all levels of the ITLB

which resulted in a completed page walk.

87H

01H

ILD_STALL.LCP

Cycles Instruction Length Decoder stalls due to

length changing prefixes: 66, 67 or REX.W (for Intel

64) instructions which change the length of the

decoded instruction.

87H

02H

ILD_STALL.MRU

Instruction Length Decoder stall cycles due to Brand

Prediction Unit (PBU) Most Recently Used (MRU)

bypass.

87H

04H

ILD_STALL.IQ_FULL

Stall cycles due to a full instruction queue.

87H

08H

ILD_STALL.REGEN

Counts the number of regen stalls.

87H

0FH

ILD_STALL.ANY

Counts any cycles the Instruction Length Decoder is

stalled.

88H

01H

BR_INST_EXEC.COND

Counts the number of conditional near branch

instructions executed, but not necessarily retired.

Table 19-17. Non-Architectural Performance Events In the Processor Core for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment