19-64 Vol. 3B

PERFORMANCE-MONITORING EVENTS

42H

08H

L1D_CACHE_LOCK.M_STATE

Counts L1 data cache retired load locks that hit the

target cache line in the modified state.

Counter 0, 1 only.

43H

01H

L1D_ALL_REF.ANY

Counts all references (uncached, speculated and

retired) to the L1 data cache, including all loads and

stores with any memory types. The event counts

memory accesses only when they are actually

performed. For example, a load blocked by unknown

store address and later performed is only counted

once.

The event does not

include non-memory

accesses, such as I/O

accesses. Counter 0, 1

only.

43H

02H

L1D_ALL_REF.CACHEABLE

Counts all data reads and writes (speculated and

retired) from cacheable memory, including locked

operations.

Counter 0, 1 only.

49H

01H

DTLB_MISSES.ANY

Counts the number of misses in the STLB which

causes a page walk.

49H

02H

DTLB_MISSES.WALK_COMPLET

ED

Counts number of misses in the STLB which

resulted in a completed page walk.

49H

10H

DTLB_MISSES.STLB_HIT

Counts the number of DTLB first level misses that

hit in the second level TLB. This event is only

relevant if the core contains multiple DTLB levels.

49H

20H

DTLB_MISSES.PDE_MISS

Number of DTLB misses caused by low part of

address, includes references to 2M pages because

2M pages do not use the PDE.

49H

80H

DTLB_MISSES.LARGE_WALK_C

OMPLETED

Counts number of misses in the STLB which

resulted in a completed page walk for large pages.

4CH

01H

LOAD_HIT_PRE

Counts load operations sent to the L1 data cache

while a previous SSE prefetch instruction to the

same cache line has started prefetching but has not

yet finished.

4EH

01H

L1D_PREFETCH.REQUESTS

Counts number of hardware prefetch requests

dispatched out of the prefetch FIFO.

4EH

02H

L1D_PREFETCH.MISS

Counts number of hardware prefetch requests that

miss the L1D. There are two prefetchers in the L1D.

A streamer, which predicts lines sequentially after

this one should be fetched, and the IP prefetcher

that remembers access patterns for the current

instruction. The streamer prefetcher stops on an

L1D hit, while the IP prefetcher does not.

4EH

04H

L1D_PREFETCH.TRIGGERS

Counts number of prefetch requests triggered by

the Finite State Machine and pushed into the

prefetch FIFO. Some of the prefetch requests are

dropped due to overwrites or competition between

the IP index prefetcher and streamer prefetcher.

The prefetch FIFO contains 4 entries.

51H

01H

L1D.REPL

Counts the number of lines brought into the L1 data

cache.

Counter 0, 1 only.

51H

02H

L1D.M_REPL

Counts the number of modified lines brought into

the L1 data cache.

Counter 0, 1 only.

51H

04H

L1D.M_EVICT

Counts the number of modified lines evicted from

the L1 data cache due to replacement.

Counter 0, 1 only.

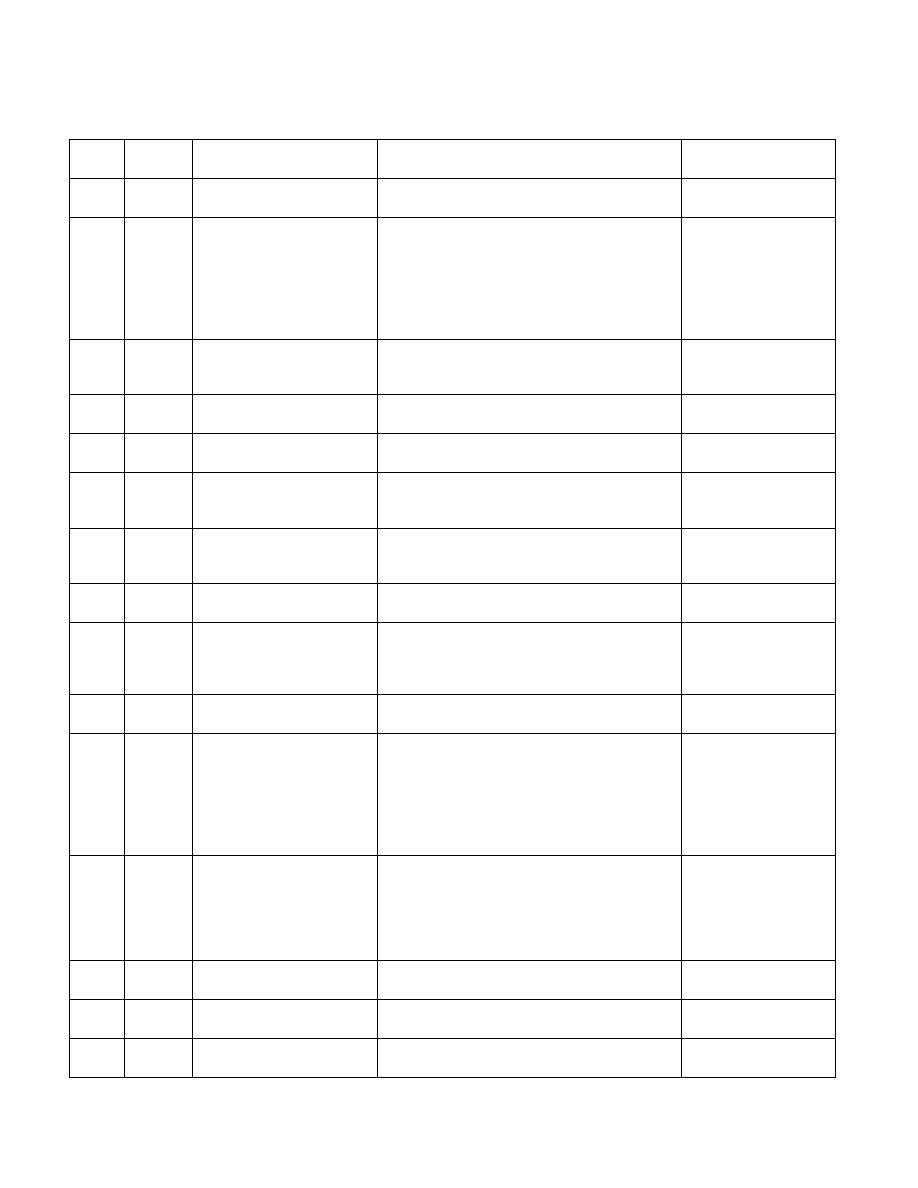

Table 19-17. Non-Architectural Performance Events In the Processor Core for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment