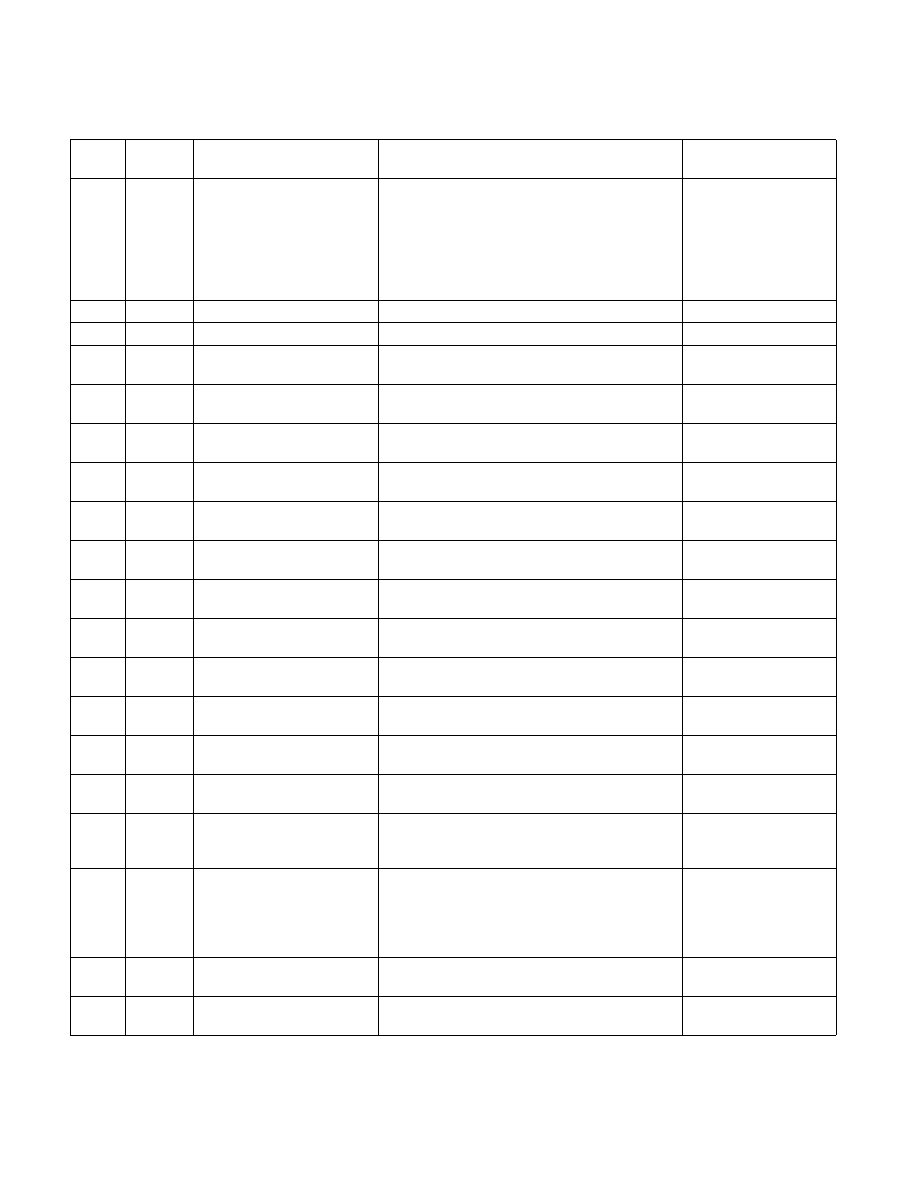

Vol. 3B 19-59

PERFORMANCE-MONITORING EVENTS

10H

01H

FP_COMP_OPS_EXE.X87

Counts the number of FP Computational Uops

Executed. The number of FADD, FSUB, FCOM,

FMULs, integer MULs and IMULs, FDIVs, FPREMs,

FSQRTS, integer DIVs, and IDIVs. This event does

not distinguish an FADD used in the middle of a

transcendental flow from a separate FADD

instruction.

10H

02H

FP_COMP_OPS_EXE.MMX

Counts number of MMX Uops executed.

10H

04H

FP_COMP_OPS_EXE.SSE_FP

Counts number of SSE and SSE2 FP uops executed.

10H

08H

FP_COMP_OPS_EXE.SSE2_INT

EGER

Counts number of SSE2 integer uops executed.

10H

10H

FP_COMP_OPS_EXE.SSE_FP_P

ACKED

Counts number of SSE FP packed uops executed.

10H

20H

FP_COMP_OPS_EXE.SSE_FP_S

CALAR

Counts number of SSE FP scalar uops executed.

10H

40H

FP_COMP_OPS_EXE.SSE_SING

LE_PRECISION

Counts number of SSE* FP single precision uops

executed.

10H

80H

FP_COMP_OPS_EXE.SSE_DOU

BLE_PRECISION

Counts number of SSE* FP double precision uops

executed.

12H

01H

SIMD_INT_128.PACKED_MPY

Counts number of 128 bit SIMD integer multiply

operations.

12H

02H

SIMD_INT_128.PACKED_SHIFT Counts number of 128 bit SIMD integer shift

operations.

12H

04H

SIMD_INT_128.PACK

Counts number of 128 bit SIMD integer pack

operations.

12H

08H

SIMD_INT_128.UNPACK

Counts number of 128 bit SIMD integer unpack

operations.

12H

10H

SIMD_INT_128.PACKED_LOGIC

AL

Counts number of 128 bit SIMD integer logical

operations.

12H

20H

SIMD_INT_128.PACKED_ARITH Counts number of 128 bit SIMD integer arithmetic

operations.

12H

40H

SIMD_INT_128.SHUFFLE_MOV

E

Counts number of 128 bit SIMD integer shuffle and

move operations.

13H

01H

LOAD_DISPATCH.RS

Counts number of loads dispatched from the

Reservation Station that bypass the Memory Order

Buffer.

13H

02H

LOAD_DISPATCH.RS_DELAYED Counts the number of delayed RS dispatches at the

stage latch. If an RS dispatch cannot bypass to LB, it

has another chance to dispatch from the one-cycle

delayed staging latch before it is written into the

LB.

13H

04H

LOAD_DISPATCH.MOB

Counts the number of loads dispatched from the

Reservation Station to the Memory Order Buffer.

13H

07H

LOAD_DISPATCH.ANY

Counts all loads dispatched from the Reservation

Station.

Table 19-17. Non-Architectural Performance Events In the Processor Core for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment