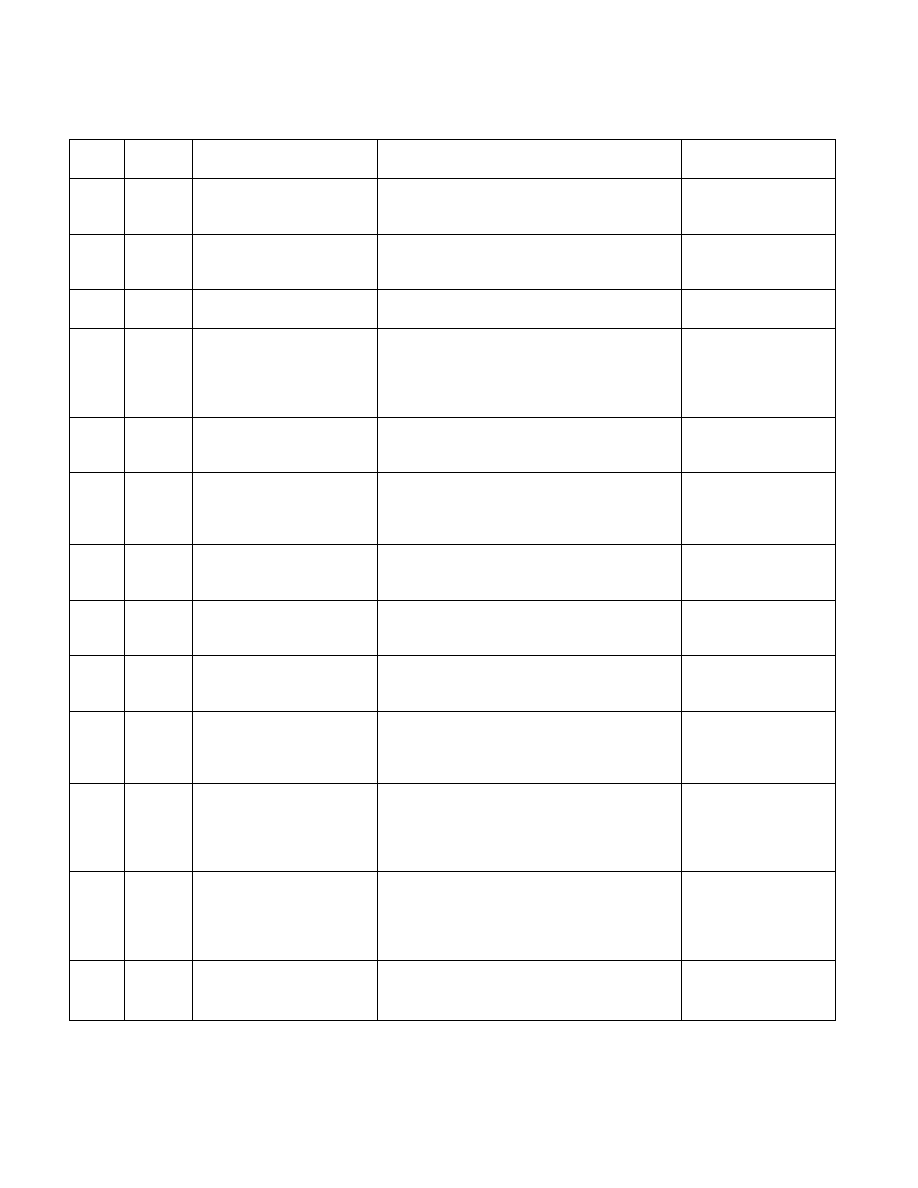

19-58 Vol. 3B

PERFORMANCE-MONITORING EVENTS

0BH

01H

MEM_INST_RETIRED.LOADS

Counts the number of instructions with an

architecturally-visible load retired on the

architected path.

0BH

02H

MEM_INST_RETIRED.STORES

Counts the number of instructions with an

architecturally-visible store retired on the

architected path.

0BH

10H

MEM_INST_RETIRED.LATENCY

_ABOVE_THRESHOLD

Counts the number of instructions exceeding the

latency specified with ld_lat facility.

In conjunction with ld_lat

facility.

0CH

01H

MEM_STORE_RETIRED.DTLB_

MISS

The event counts the number of retired stores that

missed the DTLB. The DTLB miss is not counted if

the store operation causes a fault. Does not counter

prefetches. Counts both primary and secondary

misses to the TLB.

0EH

01H

UOPS_ISSUED.ANY

Counts the number of Uops issued by the Register

Allocation Table to the Reservation Station, i.e. the

UOPs issued from the front end to the back end.

0EH

01H

UOPS_ISSUED.STALLED_CYCLE

S

Counts the number of cycles no Uops issued by the

Register Allocation Table to the Reservation

Station, i.e. the UOPs issued from the front end to

the back end.

Set “invert=1, cmask =

1“.

0EH

02H

UOPS_ISSUED.FUSED

Counts the number of fused Uops that were issued

from the Register Allocation Table to the

Reservation Station.

0FH

01H

MEM_UNCORE_RETIRED.L3_D

ATA_MISS_UNKNOWN

Counts number of memory load instructions retired

where the memory reference missed L3 and data

source is unknown.

Available only for CPUID

signature 06_2EH.

0FH

02H

MEM_UNCORE_RETIRED.OTHE

R_CORE_L2_HITM

Counts number of memory load instructions retired

where the memory reference hit modified data in a

sibling core residing on the same socket.

0FH

08H

MEM_UNCORE_RETIRED.REMO

TE_CACHE_LOCAL_HOME_HIT

Counts number of memory load instructions retired

where the memory reference missed the L1, L2 and

L3 caches and HIT in a remote socket's cache. Only

counts locally homed lines.

0FH

10H

MEM_UNCORE_RETIRED.REMO

TE_DRAM

Counts number of memory load instructions retired

where the memory reference missed the L1, L2 and

L3 caches and was remotely homed. This includes

both DRAM access and HITM in a remote socket's

cache for remotely homed lines.

0FH

20H

MEM_UNCORE_RETIRED.LOCA

L_DRAM

Counts number of memory load instructions retired

where the memory reference missed the L1, L2 and

L3 caches and required a local socket memory

reference. This includes locally homed cachelines

that were in a modified state in another socket.

0FH

80H

MEM_UNCORE_RETIRED.UNCA

CHEABLE

Counts number of memory load instructions retired

where the memory reference missed the L1, L2 and

L3 caches and to perform I/O.

Available only for CPUID

signature 06_2EH.

Table 19-17. Non-Architectural Performance Events In the Processor Core for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment