Vol. 3B 19-55

PERFORMANCE-MONITORING EVENTS

Non-architectural Performance monitoring events that are located in the uncore sub-system are implementation

specific between different platforms using processors based on Intel microarchitecture code name Sandy Bridge.

Processors with CPUID signature of DisplayFamily_DisplayModel 06_2AH support performance events listed in

Table 19-16.

D1H

20H

MEM_LOAD_UOPS_RETIRED.LL

C_MISS

Additional Configuration: Disable BL bypass and direct2core. Supports PEBS.

D2H

01H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_MISS

Additional Configuration: Disable bypass. Supports PEBS.

D2H

02H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_HIT

Additional Configuration: Disable bypass. Supports PEBS.

D2H

04H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_HITM

Additional Configuration: Disable bypass. Supports PEBS.

D2H

08H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_NONE

Additional Configuration: Disable bypass. Supports PEBS.

D3H

01H

MEM_LOAD_UOPS_LLC_MISS_

RETIRED.LOCAL_DRAM

Retired load uops which data sources were data

missed LLC but serviced by local DRAM. Supports

PEBS.

Disable BL bypass and

direct2core (see MSR

3C9H).

D3H

04H

MEM_LOAD_UOPS_LLC_MISS_

RETIRED.REMOTE_DRAM

Retired load uops which data sources were data

missed LLC but serviced by remote DRAM. Supports

PEBS.

Disable BL bypass and

direct2core (see MSR

3C9H).

B7H/BB

H

01H

OFF_CORE_RESPONSE_N

Sub-events of OFF_CORE_RESPONSE_N (suffix N = 0,

1) programmed using MSR 01A6H/01A7H with values

shown in the comment column.

OFFCORE_RESPONSE.DEMAND_CODE_RD.LLC_MISS.ANY_RESPONSE_N

3FFFC00004H

OFFCORE_RESPONSE.DEMAND_CODE_RD.LLC_MISS.LOCAL_DRAM_N

600400004H

OFFCORE_RESPONSE.DEMAND_CODE_RD.LLC_MISS.REMOTE_DRAM_N

67F800004H

OFFCORE_RESPONSE.DEMAND_CODE_RD.LLC_MISS.REMOTE_HIT_FWD_N

87F800004H

OFFCORE_RESPONSE.DEMAND_CODE_RD.LLC_MISS.REMOTE_HITM_N

107FC00004H

OFFCORE_RESPONSE.DEMAND_DATA_RD.LLC_MISS.ANY_DRAM_N

67FC00001H

OFFCORE_RESPONSE.DEMAND_DATA_RD.LLC_MISS.ANY_RESPONSE_N

3F803C0001H

OFFCORE_RESPONSE.DEMAND_DATA_RD.LLC_MISS.LOCAL_DRAM_N

600400001H

OFFCORE_RESPONSE.DEMAND_DATA_RD.LLC_MISS.REMOTE_DRAM_N

67F800001H

OFFCORE_RESPONSE.DEMAND_DATA_RD.LLC_MISS.REMOTE_HIT_FWD_N

87F800001H

OFFCORE_RESPONSE.DEMAND_DATA_RD.LLC_MISS.REMOTE_HITM_N

107FC00001H

OFFCORE_RESPONSE.PF_L2_CODE_RD.LLC_MISS.ANY_RESPONSE_N

3F803C0040H

OFFCORE_RESPONSE.PF_L2_DATA_RD.LLC_MISS.ANY_DRAM_N

67FC00010H

OFFCORE_RESPONSE.PF_L2_DATA_RD.LLC_MISS.ANY_RESPONSE_N

3F803C0010H

OFFCORE_RESPONSE.PF_L2_DATA_RD.LLC_MISS.LOCAL_DRAM_N

600400010H

OFFCORE_RESPONSE.PF_L2_DATA_RD.LLC_MISS.REMOTE_DRAM_N

67F800010H

OFFCORE_RESPONSE.PF_L2_DATA_RD.LLC_MISS.REMOTE_HIT_FWD_N

87F800010H

OFFCORE_RESPONSE.PF_L2_DATA_RD.LLC_MISS.REMOTE_HITM_N

107FC00010H

OFFCORE_RESPONSE.PF_LLC_CODE_RD.LLC_MISS.ANY_RESPONSE_N

3FFFC00200H

OFFCORE_RESPONSE.PF_LLC_DATA_RD.LLC_MISS.ANY_RESPONSE_N

3FFFC00080H

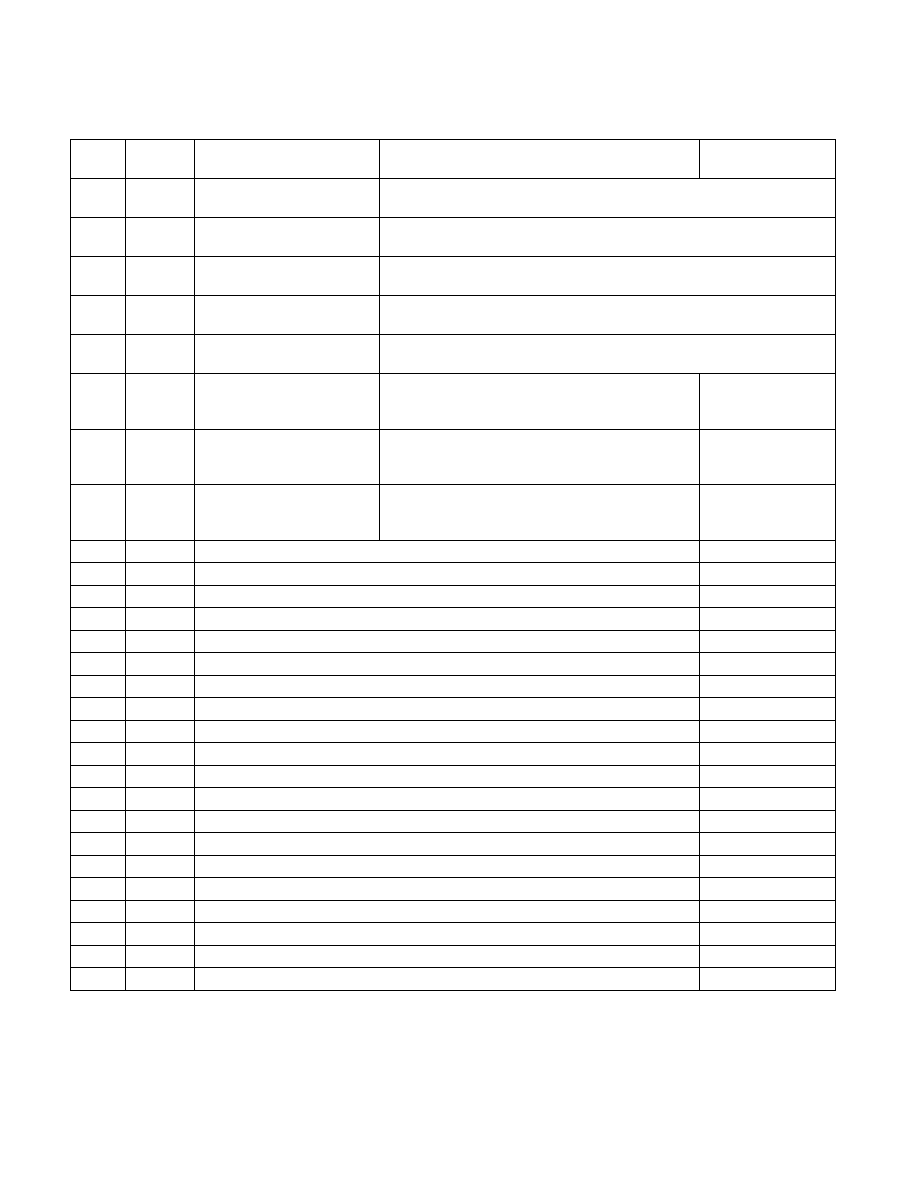

Table 19-15. Non-Architectural Performance Events Applicable only to the Processor Core of

Intel® Xeon® Processor E5 Family

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment