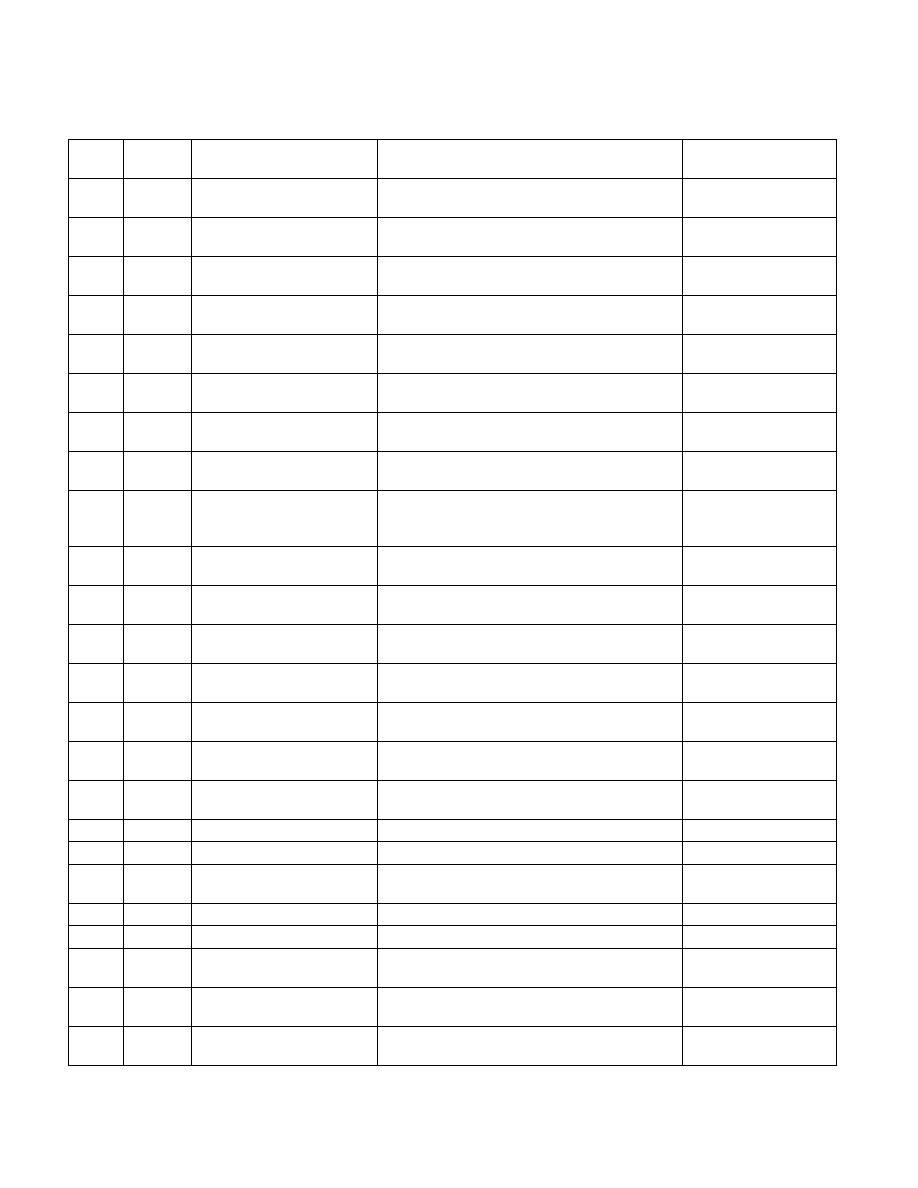

19-48 Vol. 3B

PERFORMANCE-MONITORING EVENTS

89H

84H

BR_MISP_EXEC.TAKEN_INDIRE

CT_JUMP_NON_CALL_RET

Taken speculative and retired mispredicted indirect

branches excluding calls and returns.

89H

88H

BR_MISP_EXEC.TAKEN_RETUR

N_NEAR

Taken speculative and retired mispredicted indirect

branches that are returns.

89H

90H

BR_MISP_EXEC.TAKEN_DIRECT

_NEAR_CALL

Taken speculative and retired mispredicted direct

near calls.

89H

A0H

BR_MISP_EXEC.TAKEN_INDIRE

CT_NEAR_CALL

Taken speculative and retired mispredicted indirect

near calls.

89H

C1H

BR_MISP_EXEC.ALL_CONDITIO

NAL

Speculative and retired mispredicted conditional

branches.

89H

C4H

BR_MISP_EXEC.ALL_INDIRECT

_JUMP_NON_CALL_RET

Speculative and retired mispredicted indirect

branches excluding calls and returns.

89H

D0H

BR_MISP_EXEC.ALL_NEAR_CA

LL

Speculative and retired mispredicted direct near

calls.

89H

FFH

BR_MISP_EXEC.ALL_BRANCHE

S

Speculative and retired mispredicted branches.

9CH

01H

IDQ_UOPS_NOT_DELIVERED.C

ORE

Count issue pipeline slots where no uop was

delivered from the front end to the back end when

there is no back-end stall.

Use Cmask to qualify uop

b/w.

A1H

01H

UOPS_DISPATCHED_PORT.POR

T_0

Cycles which a Uop is dispatched on port 0.

A1H

02H

UOPS_DISPATCHED_PORT.POR

T_1

Cycles which a Uop is dispatched on port 1.

A1H

0CH

UOPS_DISPATCHED_PORT.POR

T_2

Cycles which a Uop is dispatched on port 2.

A1H

30H

UOPS_DISPATCHED_PORT.POR

T_3

Cycles which a Uop is dispatched on port 3.

A1H

40H

UOPS_DISPATCHED_PORT.POR

T_4

Cycles which a Uop is dispatched on port 4.

A1H

80H

UOPS_DISPATCHED_PORT.POR

T_5

Cycles which a Uop is dispatched on port 5.

A2H

01H

RESOURCE_STALLS.ANY

Cycles Allocation is stalled due to Resource Related

reason.

A2H

02H

RESOURCE_STALLS.LB

Counts the cycles of stall due to lack of load buffers.

A2H

04H

RESOURCE_STALLS.RS

Cycles stalled due to no eligible RS entry available.

A2H

08H

RESOURCE_STALLS.SB

Cycles stalled due to no store buffers available (not

including draining form sync).

A2H

10H

RESOURCE_STALLS.ROB

Cycles stalled due to re-order buffer full.

A2H

20H

RESOURCE_STALLS.FCSW

Cycles stalled due to writing the FPU control word.

A3H

01H

CYCLE_ACTIVITY.CYCLES_L2_P

ENDING

Cycles with pending L2 miss loads. Set AnyThread

to count per core.

A3H

02H

CYCLE_ACTIVITY.CYCLES_L1D_

PENDING

Cycles with pending L1 cache miss loads. Set

AnyThread to count per core.

PMC2 only.

A3H

04H

CYCLE_ACTIVITY.CYCLES_NO_

DISPATCH

Cycles of dispatch stalls. Set AnyThread to count per

core.

PMC0-3 only.

Table 19-13. Non-Architectural Performance Events In the Processor Core Common to 2nd Generation Intel® Core™

i7-2xxx, Intel® Core™ i5-2xxx, Intel® Core™ i3-2xxx Processor Series and Intel® Xeon® Processors E3 and E5 Family

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment