19-46 Vol. 3B

PERFORMANCE-MONITORING EVENTS

51H

08H

L1D.ALL_M_REPLACEMENT

Cache lines in M state evicted out of L1D due to

Snoop HitM or dirty line replacement.

59H

20H

PARTIAL_RAT_STALLS.FLAGS_

MERGE_UOP

Increments the number of flags-merge uops in flight

each cycle. Set Cmask = 1 to count cycles.

59H

40H

PARTIAL_RAT_STALLS.SLOW_

LEA_WINDOW

Cycles with at least one slow LEA uop allocated.

59H

80H

PARTIAL_RAT_STALLS.MUL_SI

NGLE_UOP

Number of Multiply packed/scalar single precision

uops allocated.

5BH

0CH

RESOURCE_STALLS2.ALL_FL_

EMPTY

Cycles stalled due to free list empty.

PMC0-3 only regardless

HTT.

5BH

0FH

RESOURCE_STALLS2.ALL_PRF

_CONTROL

Cycles stalled due to control structures full for

physical registers.

5BH

40H

RESOURCE_STALLS2.BOB_FUL

L

Cycles Allocator is stalled due Branch Order Buffer.

5BH

4FH

RESOURCE_STALLS2.OOO_RS

RC

Cycles stalled due to out of order resources full.

5CH

01H

CPL_CYCLES.RING0

Unhalted core cycles when the thread is in ring 0.

Use Edge to count

transition.

5CH

02H

CPL_CYCLES.RING123

Unhalted core cycles when the thread is not in ring

0.

5EH

01H

RS_EVENTS.EMPTY_CYCLES

Cycles the RS is empty for the thread.

60H

01H

OFFCORE_REQUESTS_OUTSTA

NDING.DEMAND_DATA_RD

Offcore outstanding Demand Data Read

transactions in SQ to uncore. Set Cmask=1 to count

cycles.

60H

04H

OFFCORE_REQUESTS_OUTSTA

NDING.DEMAND_RFO

Offcore outstanding RFO store transactions in SQ to

uncore. Set Cmask=1 to count cycles.

60H

08H

OFFCORE_REQUESTS_OUTSTA

NDING.ALL_DATA_RD

Offcore outstanding cacheable data read

transactions in SQ to uncore. Set Cmask=1 to count

cycles.

63H

01H

LOCK_CYCLES.SPLIT_LOCK_UC

_LOCK_DURATION

Cycles in which the L1D and L2 are locked, due to a

UC lock or split lock.

63H

02H

LOCK_CYCLES.CACHE_LOCK_D

URATION

Cycles in which the L1D is locked.

79H

02H

IDQ.EMPTY

Counts cycles the IDQ is empty.

79H

04H

IDQ.MITE_UOPS

Increment each cycle # of uops delivered to IDQ

from MITE path. Set Cmask = 1 to count cycles.

Can combine Umask 04H

and 20H.

79H

08H

IDQ.DSB_UOPS

Increment each cycle. # of uops delivered to IDQ

from DSB path. Set Cmask = 1 to count cycles.

Can combine Umask 08H

and 10H.

79H

10H

IDQ.MS_DSB_UOPS

Increment each cycle # of uops delivered to IDQ

when MS busy by DSB. Set Cmask = 1 to count

cycles MS is busy. Set Cmask=1 and Edge =1 to

count MS activations.

Can combine Umask 08H

and 10H.

79H

20H

IDQ.MS_MITE_UOPS

Increment each cycle # of uops delivered to IDQ

when MS is busy by MITE. Set Cmask = 1 to count

cycles.

Can combine Umask 04H

and 20H.

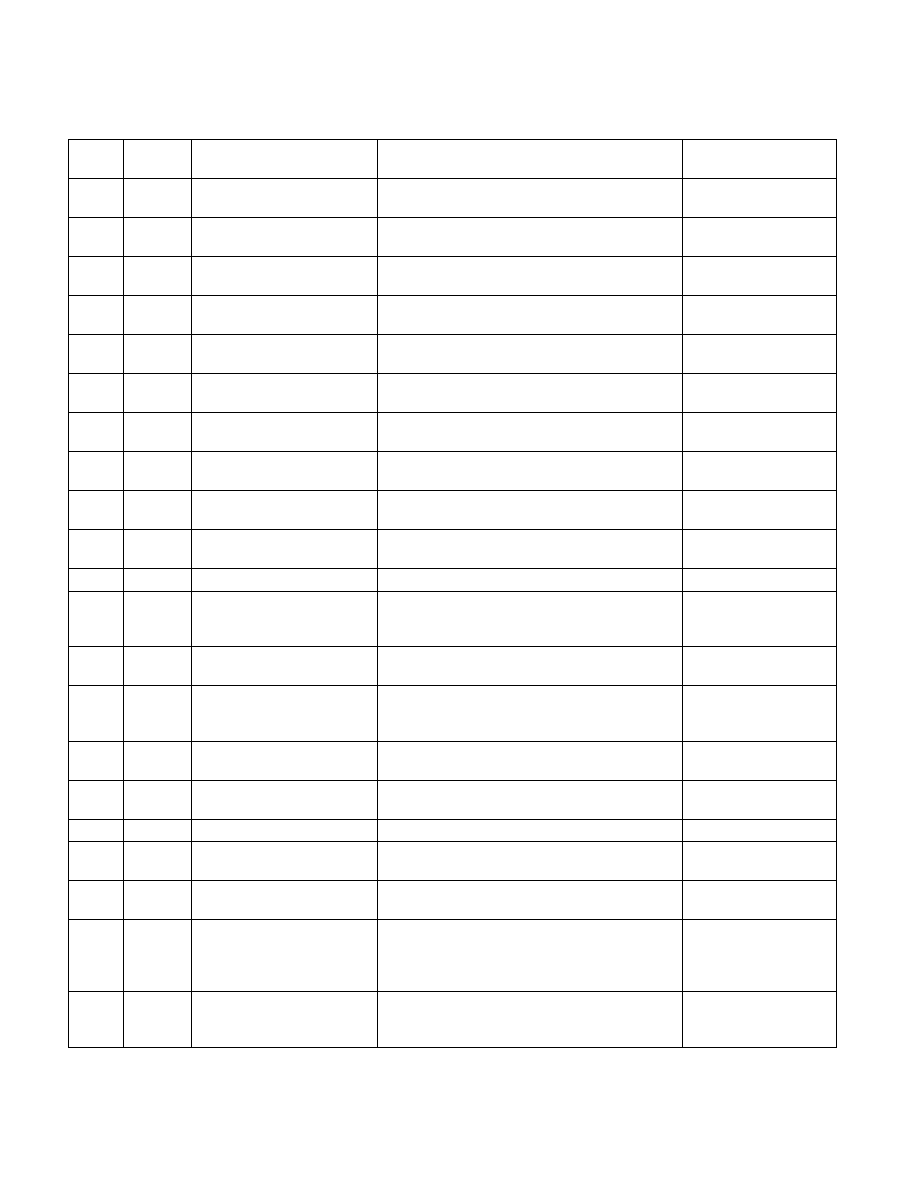

Table 19-13. Non-Architectural Performance Events In the Processor Core Common to 2nd Generation Intel® Core™

i7-2xxx, Intel® Core™ i5-2xxx, Intel® Core™ i3-2xxx Processor Series and Intel® Xeon® Processors E3 and E5 Family

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment