19-44 Vol. 3B

PERFORMANCE-MONITORING EVENTS

0EH

01H

UOPS_ISSUED.ANY

Increments each cycle the # of Uops issued by the

RAT to RS. Set Cmask = 1, Inv = 1, Any= 1to count

stalled cycles of this core.

Set Cmask = 1, Inv = 1to

count stalled cycles.

10H

01H

FP_COMP_OPS_EXE.X87

Counts number of X87 uops executed.

10H

10H

FP_COMP_OPS_EXE.SSE_FP_P

ACKED_DOUBLE

Counts number of SSE* double precision FP packed

uops executed.

10H

20H

FP_COMP_OPS_EXE.SSE_FP_S

CALAR_SINGLE

Counts number of SSE* single precision FP scalar

uops executed.

10H

40H

FP_COMP_OPS_EXE.SSE_PACK

ED SINGLE

Counts number of SSE* single precision FP packed

uops executed.

10H

80H

FP_COMP_OPS_EXE.SSE_SCAL

AR_DOUBLE

Counts number of SSE* double precision FP scalar

uops executed.

11H

01H

SIMD_FP_256.PACKED_SINGLE Counts 256-bit packed single-precision floating-

point instructions.

11H

02H

SIMD_FP_256.PACKED_DOUBL

E

Counts 256-bit packed double-precision floating-

point instructions.

14H

01H

ARITH.FPU_DIV_ACTIVE

Cycles that the divider is active, includes INT and FP.

Set 'edge =1, cmask=1' to count the number of

divides.

17H

01H

INSTS_WRITTEN_TO_IQ.INSTS Counts the number of instructions written into the

IQ every cycle.

24H

01H

L2_RQSTS.DEMAND_DATA_RD

_HIT

Demand Data Read requests that hit L2 cache.

24H

03H

L2_RQSTS.ALL_DEMAND_DAT

A_RD

Counts any demand and L1 HW prefetch data load

requests to L2.

24H

04H

L2_RQSTS.RFO_HITS

Counts the number of store RFO requests that hit

the L2 cache.

24H

08H

L2_RQSTS.RFO_MISS

Counts the number of store RFO requests that miss

the L2 cache.

24H

0CH

L2_RQSTS.ALL_RFO

Counts all L2 store RFO requests.

24H

10H

L2_RQSTS.CODE_RD_HIT

Number of instruction fetches that hit the L2 cache.

24H

20H

L2_RQSTS.CODE_RD_MISS

Number of instruction fetches that missed the L2

cache.

24H

30H

L2_RQSTS.ALL_CODE_RD

Counts all L2 code requests.

24H

40H

L2_RQSTS.PF_HIT

Requests from L2 Hardware prefetcher that hit L2.

24H

80H

L2_RQSTS.PF_MISS

Requests from L2 Hardware prefetcher that missed

L2.

24H

C0H

L2_RQSTS.ALL_PF

Any requests from L2 Hardware prefetchers.

27H

01H

L2_STORE_LOCK_RQSTS.MISS RFOs that miss cache lines.

27H

04H

L2_STORE_LOCK_RQSTS.HIT_

E

RFOs that hit cache lines in E state.

27H

08H

L2_STORE_LOCK_RQSTS.HIT_

M

RFOs that hit cache lines in M state.

27H

0FH

L2_STORE_LOCK_RQSTS.ALL

RFOs that access cache lines in any state.

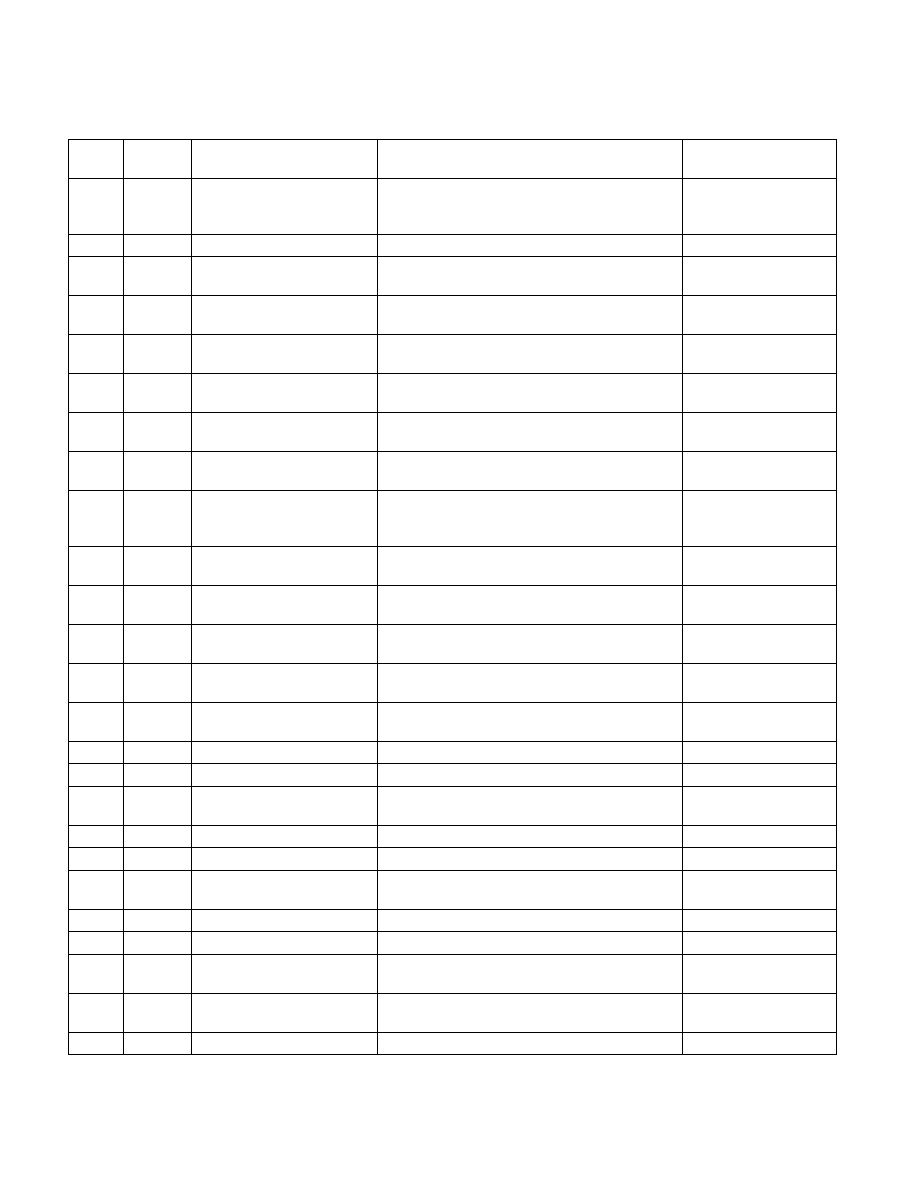

Table 19-13. Non-Architectural Performance Events In the Processor Core Common to 2nd Generation Intel® Core™

i7-2xxx, Intel® Core™ i5-2xxx, Intel® Core™ i3-2xxx Processor Series and Intel® Xeon® Processors E3 and E5 Family

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment