19-36 Vol. 3B

PERFORMANCE-MONITORING EVENTS

49H

02H

DTLB_STORE_MISSES.WALK_CO

MPLETED

Miss in all TLB levels causes a page walk that

completes of any page size (4K/2M/4M/1G).

49H

04H

DTLB_STORE_MISSES.WALK_DUR

ATION

Cycles PMH is busy with this walk.

49H

10H

DTLB_STORE_MISSES.STLB_HIT

Store operations that miss the first TLB level but hit

the second and do not cause page walks.

4CH

01H

LOAD_HIT_PRE.SW_PF

Non-SW-prefetch load dispatches that hit fill buffer

allocated for S/W prefetch.

4CH

02H

LOAD_HIT_PRE.HW_PF

Non-SW-prefetch load dispatches that hit fill buffer

allocated for H/W prefetch.

51H

01H

L1D.REPLACEMENT

Counts the number of lines brought into the L1 data

cache.

58H

04H

MOVE_ELIMINATION.INT_NOT_EL

IMINATED

Number of integer Move Elimination candidate uops

that were not eliminated.

58H

08H

MOVE_ELIMINATION.SIMD_NOT_E

LIMINATED

Number of SIMD Move Elimination candidate uops

that were not eliminated.

58H

01H

MOVE_ELIMINATION.INT_ELIMINA

TED

Number of integer Move Elimination candidate uops

that were eliminated.

58H

02H

MOVE_ELIMINATION.SIMD_ELIMIN

ATED

Number of SIMD Move Elimination candidate uops

that were eliminated.

5CH

01H

CPL_CYCLES.RING0

Unhalted core cycles when the thread is in ring 0.

Use Edge to count

transition.

5CH

02H

CPL_CYCLES.RING123

Unhalted core cycles when the thread is not in ring

0.

5EH

01H

RS_EVENTS.EMPTY_CYCLES

Cycles the RS is empty for the thread.

5FH

04H

DTLB_LOAD_MISSES.STLB_HIT

Counts load operations that missed 1st level DTLB

but hit the 2nd level.

60H

01H

OFFCORE_REQUESTS_OUTSTAN

DING.DEMAND_DATA_RD

Offcore outstanding Demand Data Read

transactions in SQ to uncore. Set Cmask=1 to count

cycles.

60H

02H

OFFCORE_REQUESTS_OUTSTAN

DING.DEMAND_CODE_RD

Offcore outstanding Demand Code Read

transactions in SQ to uncore. Set Cmask=1 to count

cycles.

60H

04H

OFFCORE_REQUESTS_OUTSTAN

DING.DEMAND_RFO

Offcore outstanding RFO store transactions in SQ to

uncore. Set Cmask=1 to count cycles.

60H

08H

OFFCORE_REQUESTS_OUTSTAN

DING.ALL_DATA_RD

Offcore outstanding cacheable data read

transactions in SQ to uncore. Set Cmask=1 to count

cycles.

63H

01H

LOCK_CYCLES.SPLIT_LOCK_UC_L

OCK_DURATION

Cycles in which the L1D and L2 are locked, due to a

UC lock or split lock.

63H

02H

LOCK_CYCLES.CACHE_LOCK_DUR

ATION

Cycles in which the L1D is locked.

79H

02H

IDQ.EMPTY

Counts cycles the IDQ is empty.

79H

04H

IDQ.MITE_UOPS

Increment each cycle # of uops delivered to IDQ

from MITE path. Set Cmask = 1 to count cycles.

Can combine Umask 04H

and 20H.

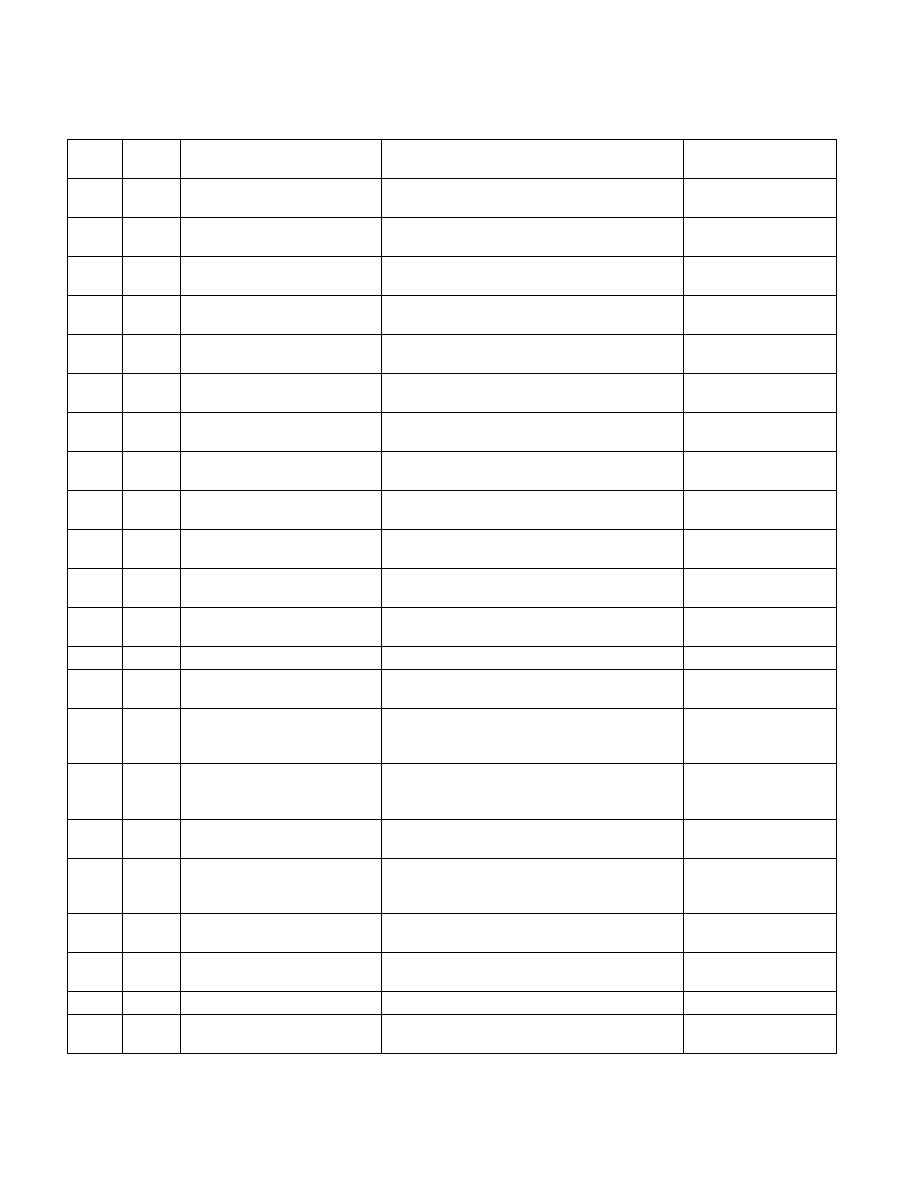

Table 19-11. Non-Architectural Performance Events In the Processor Core of

3rd Generation Intel® Core™ i7, i5, i3 Processors (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment