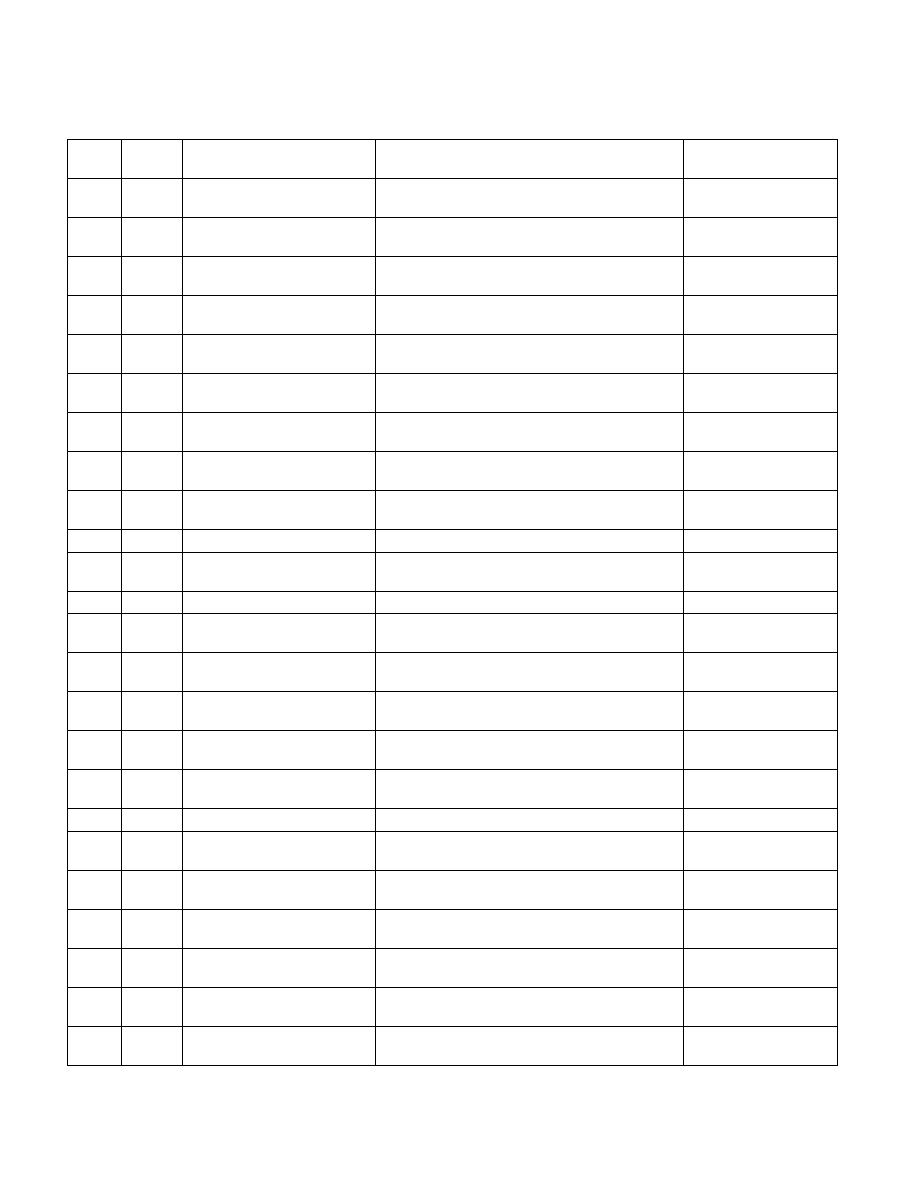

19-26 Vol. 3B

PERFORMANCE-MONITORING EVENTS

A1H

01H

UOPS_EXECUTED_PORT.PORT_

0

Cycles which a uop is dispatched on port 0 in this

thread.

Set AnyThread to count

per core.

A1H

02H

UOPS_EXECUTED_PORT.PORT_

1

Cycles which a uop is dispatched on port 1 in this

thread.

Set AnyThread to count

per core.

A1H

04H

UOPS_EXECUTED_PORT.PORT_

2

Cycles which a uop is dispatched on port 2 in this

thread.

Set AnyThread to count

per core.

A1H

08H

UOPS_EXECUTED_PORT.PORT_

3

Cycles which a uop is dispatched on port 3 in this

thread.

Set AnyThread to count

per core.

A1H

10H

UOPS_EXECUTED_PORT.PORT_

4

Cycles which a uop is dispatched on port 4 in this

thread.

Set AnyThread to count

per core.

A1H

20H

UOPS_EXECUTED_PORT.PORT_

5

Cycles which a uop is dispatched on port 5 in this

thread.

Set AnyThread to count

per core.

A1H

40H

UOPS_EXECUTED_PORT.PORT_

6

Cycles which a uop is dispatched on port 6 in this

thread.

Set AnyThread to count

per core.

A1H

80H

UOPS_EXECUTED_PORT.PORT_

7

Cycles which a uop is dispatched on port 7 in this

thread

Set AnyThread to count

per core.

A2H

01H

RESOURCE_STALLS.ANY

Cycles allocation is stalled due to resource related

reason.

A2H

04H

RESOURCE_STALLS.RS

Cycles stalled due to no eligible RS entry available.

A2H

08H

RESOURCE_STALLS.SB

Cycles stalled due to no store buffers available (not

including draining form sync).

A2H

10H

RESOURCE_STALLS.ROB

Cycles stalled due to re-order buffer full.

A3H

01H

CYCLE_ACTIVITY.CYCLES_L2_PE

NDING

Cycles with pending L2 miss loads. Set Cmask=2 to

count cycle.

Use only when HTT is

off.

A3H

02H

CYCLE_ACTIVITY.CYCLES_LDM_

PENDING

Cycles with pending memory loads. Set Cmask=2 to

count cycle.

A3H

05H

CYCLE_ACTIVITY.STALLS_L2_PE

NDING

Number of loads missed L2.

Use only when HTT is

off.

A3H

08H

CYCLE_ACTIVITY.CYCLES_L1D_P

ENDING

Cycles with pending L1 data cache miss loads. Set

Cmask=8 to count cycle.

PMC2 only.

A3H

0CH

CYCLE_ACTIVITY.STALLS_L1D_P

ENDING

Execution stalls due to L1 data cache miss loads. Set

Cmask=0CH.

PMC2 only.

A8H

01H

LSD.UOPS

Number of uops delivered by the LSD.

AEH

01H

ITLB.ITLB_FLUSH

Counts the number of ITLB flushes, includes

4k/2M/4M pages.

B0H

01H

OFFCORE_REQUESTS.DEMAND_

DATA_RD

Demand data read requests sent to uncore.

Use only when HTT is

off.

B0H

02H

OFFCORE_REQUESTS.DEMAND_

CODE_RD

Demand code read requests sent to uncore.

Use only when HTT is

off.

B0H

04H

OFFCORE_REQUESTS.DEMAND_

RFO

Demand RFO read requests sent to uncore, including

regular RFOs, locks, ItoM.

Use only when HTT is

off.

B0H

08H

OFFCORE_REQUESTS.ALL_DATA

_RD

Data read requests sent to uncore (demand and

prefetch).

Use only when HTT is

off.

B1H

02H

UOPS_EXECUTED.CORE

Counts total number of uops to be executed per-core

each cycle.

Do not need to set ANY.

Table 19-7. Non-Architectural Performance Events in the Processor Core of

4th Generation Intel® Core™ Processors (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment