Vol. 3B 19-15

PERFORMANCE-MONITORING EVENTS

58H

08H

MOVE_ELIMINATION.SIMD_NOT_

ELIMINATED

Number of SIMD move elimination candidate uops

that were not eliminated.

58H

01H

MOVE_ELIMINATION.INT_ELIMIN

ATED

Number of integer move elimination candidate uops

that were eliminated.

58H

02H

MOVE_ELIMINATION.SIMD_ELIMI

NATED

Number of SIMD move elimination candidate uops

that were eliminated.

5CH

01H

CPL_CYCLES.RING0

Unhalted core cycles when the thread is in ring 0.

Use Edge to count

transition.

5CH

02H

CPL_CYCLES.RING123

Unhalted core cycles when the thread is not in ring 0.

5EH

01H

RS_EVENTS.EMPTY_CYCLES

Cycles the RS is empty for the thread.

60H

01H

OFFCORE_REQUESTS_OUTSTAN

DING.DEMAND_DATA_RD

Offcore outstanding demand data read transactions

in SQ to uncore. Set Cmask=1 to count cycles.

Use only when HTT is

off.

60H

02H

OFFCORE_REQUESTS_OUTSTAN

DING.DEMAND_CODE_RD

Offcore outstanding demand code read transactions

in SQ to uncore. Set Cmask=1 to count cycles.

Use only when HTT is

off.

60H

04H

OFFCORE_REQUESTS_OUTSTAN

DING.DEMAND_RFO

Offcore outstanding RFO store transactions in SQ to

uncore. Set Cmask=1 to count cycles.

Use only when HTT is

off.

60H

08H

OFFCORE_REQUESTS_OUTSTAN

DING.ALL_DATA_RD

Offcore outstanding cacheable data read

transactions in SQ to uncore. Set Cmask=1 to count

cycles.

Use only when HTT is

off.

63H

01H

LOCK_CYCLES.SPLIT_LOCK_UC_

LOCK_DURATION

Cycles in which the L1D and L2 are locked, due to a

UC lock or split lock.

63H

02H

LOCK_CYCLES.CACHE_LOCK_DU

RATION

Cycles in which the L1D is locked.

79H

02H

IDQ.EMPTY

Counts cycles the IDQ is empty.

79H

04H

IDQ.MITE_UOPS

Increment each cycle # of uops delivered to IDQ from

MITE path. Set Cmask = 1 to count cycles.

Can combine Umask 04H

and 20H.

79H

08H

IDQ.DSB_UOPS

Increment each cycle # of uops delivered to IDQ from

DSB path. Set Cmask = 1 to count cycles.

Can combine Umask 08H

and 10H.

79H

10H

IDQ.MS_DSB_UOPS

Increment each cycle # of uops delivered to IDQ

when MS_busy by DSB. Set Cmask = 1 to count

cycles. Add Edge=1 to count # of delivery.

Can combine Umask 04H,

08H.

79H

20H

IDQ.MS_MITE_UOPS

Increment each cycle # of uops delivered to IDQ

when MS_busy by MITE. Set Cmask = 1 to count

cycles.

Can combine Umask 04H,

08H.

79H

30H

IDQ.MS_UOPS

Increment each cycle # of uops delivered to IDQ from

MS by either DSB or MITE. Set Cmask = 1 to count

cycles.

Can combine Umask 04H,

08H.

79H

18H

IDQ.ALL_DSB_CYCLES_ANY_UO

PS

Counts cycles DSB is delivered at least one uops. Set

Cmask = 1.

79H

18H

IDQ.ALL_DSB_CYCLES_4_UOPS Counts cycles DSB is delivered four uops. Set Cmask

= 4.

79H

24H

IDQ.ALL_MITE_CYCLES_ANY_UO

PS

Counts cycles MITE is delivered at least one uop. Set

Cmask = 1.

79H

24H

IDQ.ALL_MITE_CYCLES_4_UOPS Counts cycles MITE is delivered four uops. Set Cmask

= 4.

79H

3CH

IDQ.MITE_ALL_UOPS

Number of uops delivered to IDQ from any path.

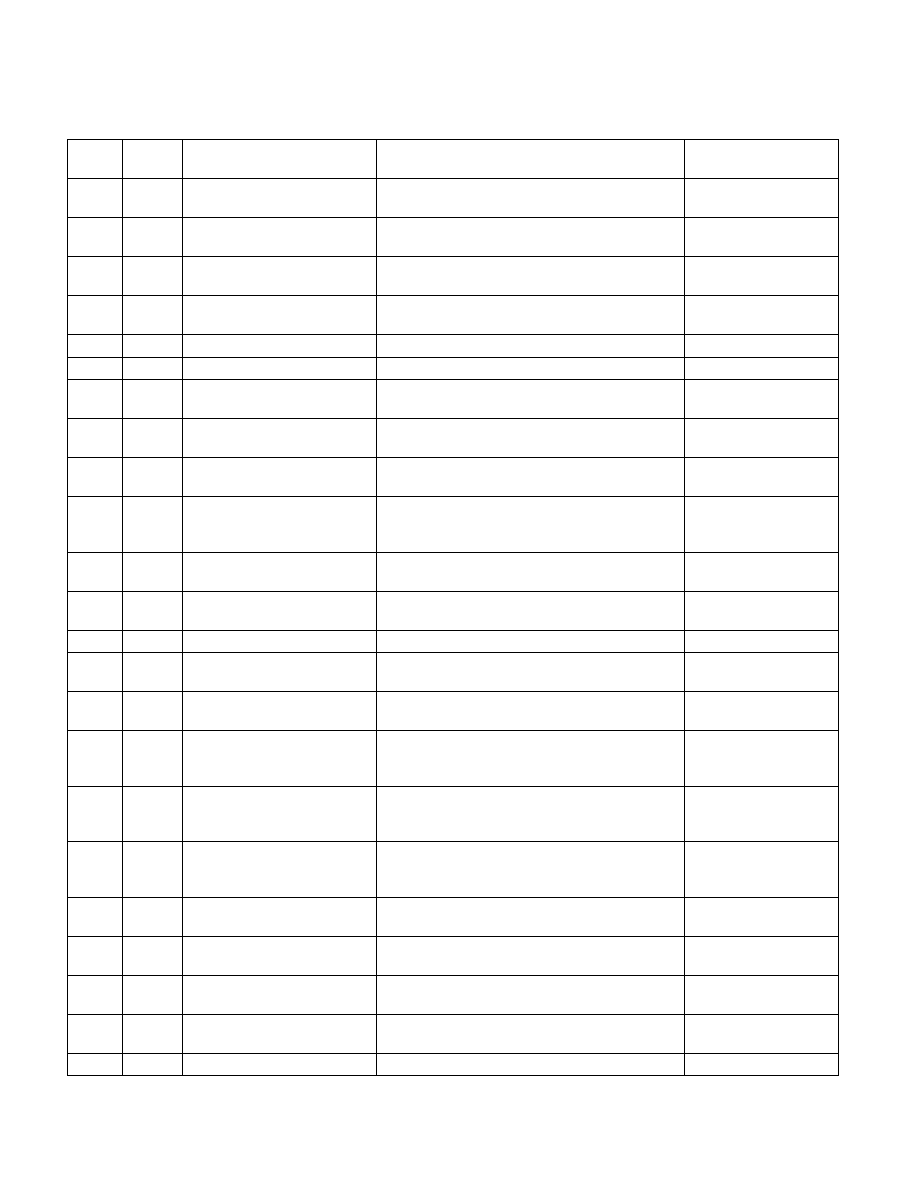

Table 19-5. Non-Architectural Performance Events of the Processor Core Supported by Broadwell

Microarchitecture (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment