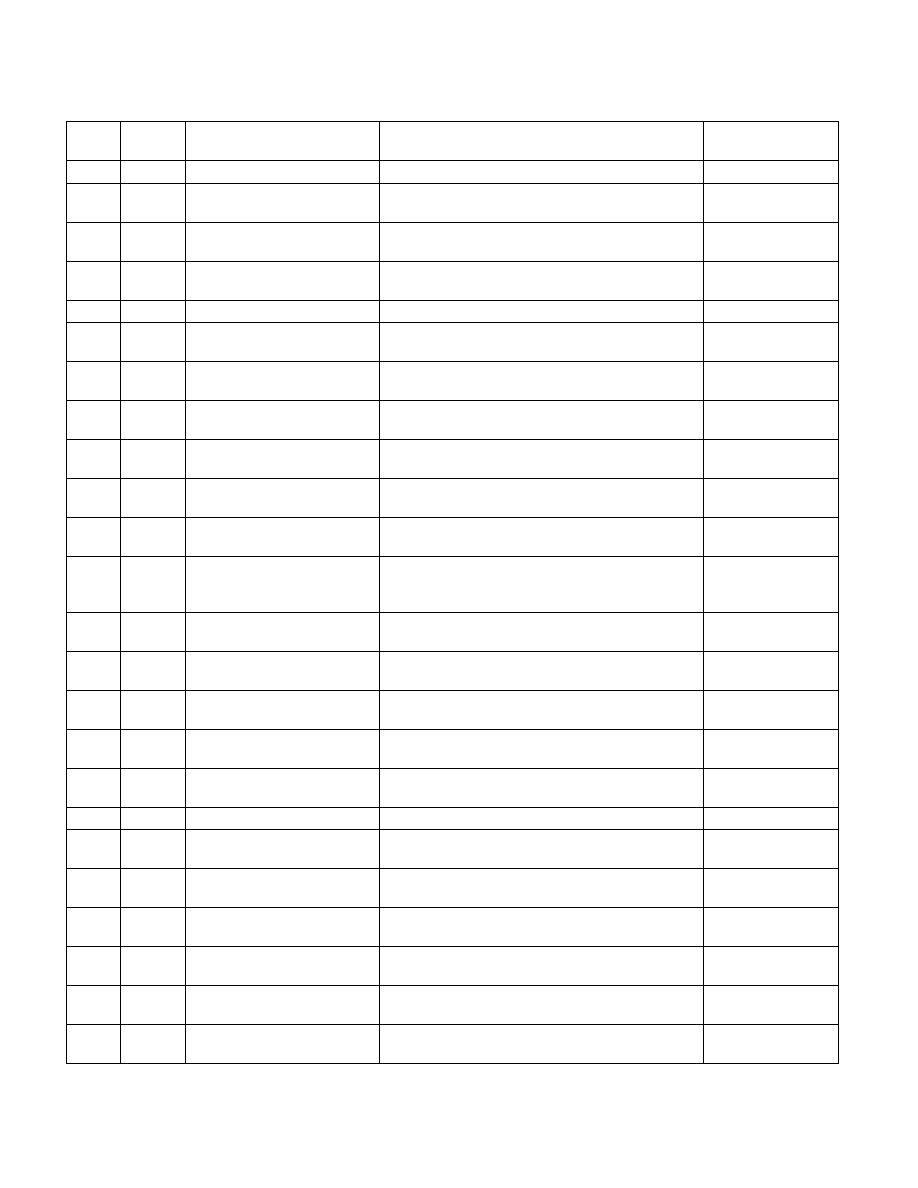

19-8 Vol. 3B

PERFORMANCE-MONITORING EVENTS

A2H

01H

RESOURCE_STALLS.ANY

Resource-related stall cycles.

A2H

08H

RESOURCE_STALLS.SB

Cycles stalled due to no store buffers available (not

including draining form sync).

A3H

01H

CYCLE_ACTIVITY.CYCLES_L2_MI

SS

Cycles while L2 cache miss demand load is outstanding. CMSK1

A3H

02H

CYCLE_ACTIVITY.CYCLES_L3_MI

SS

Cycles while L3 cache miss demand load is outstanding. CMSK2

A3H

04H

CYCLE_ACTIVITY.STALLS_TOTAL Total execution stalls.

CMSK4

A3H

05H

CYCLE_ACTIVITY.STALLS_L2_MI

SS

Execution stalls while L2 cache miss demand load is

outstanding.

CMSK5

A3H

06H

CYCLE_ACTIVITY.STALLS_L3_MI

SS

Execution stalls while L3 cache miss demand load is

outstanding.

CMSK6

A3H

08H

CYCLE_ACTIVITY.CYCLES_L1D_M

ISS

Cycles while L1 data cache miss demand load is

outstanding.

CMSK8

A3H

0CH

CYCLE_ACTIVITY.STALLS_L1D_M

ISS

Execution stalls while L1 data cache miss demand load

is outstanding.

CMSK12

A3H

10H

CYCLE_ACTIVITY.CYCLES_MEM_

ANY

Cycles while memory subsystem has an outstanding

load.

CMSK16

A3H

14H

CYCLE_ACTIVITY.STALLS_MEM_

ANY

Execution stalls while memory subsystem has an

outstanding load.

CMSK20

A6H

01H

EXE_ACTIVITY.EXE_BOUND_0_P

ORTS

Cycles for which no uops began execution, the

Reservation Station was not empty, the Store Buffer

was full and there was no outstanding load.

A6H

02H

EXE_ACTIVITY.1_PORTS_UTIL

Cycles for which one uop began execution on any port,

and the Reservation Station was not empty.

A6H

04H

EXE_ACTIVITY.2_PORTS_UTIL

Cycles for which two uops began execution, and the

Reservation Station was not empty.

A6H

08H

EXE_ACTIVITY.3_PORTS_UTIL

Cycles for which three uops began execution, and the

Reservation Station was not empty.

A6H

04H

EXE_ACTIVITY.4_PORTS_UTIL

Cycles for which four uops began execution, and the

Reservation Station was not empty.

A6H

40H

EXE_ACTIVITY.BOUND_ON_STO

RES

Cycles where the Store Buffer was full and no

outstanding load.

A8H

01H

LSD.UOPS

Number of uops delivered by the LSD.

A8H

01H

LSD.CYCLES_ACTIVE

Cycles with at least one uop delivered by the LSD and

none from the decoder.

CMSK1

A8H

01H

LSD.CYCLES_4_UOPS

Cycles with 4 uops delivered by the LSD and none from

the decoder.

CMSK4

ABH

02H

DSB2MITE_SWITCHES.PENALTY

_CYCLES

DSB-to-MITE switch true penalty cycles.

AEH

01H

ITLB.ITLB_FLUSH

Flushing of the Instruction TLB (ITLB) pages, includes

4k/2M/4M pages.

B0H

01H

OFFCORE_REQUESTS.DEMAND_

DATA_RD

Demand data read requests sent to uncore.

B0H

02H

OFFCORE_REQUESTS.DEMAND_

CODE_RD

Demand code read requests sent to uncore.

Table 19-3. Non-Architectural Performance Events of the Processor Core Supported by Skylake Microarchitecture

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment