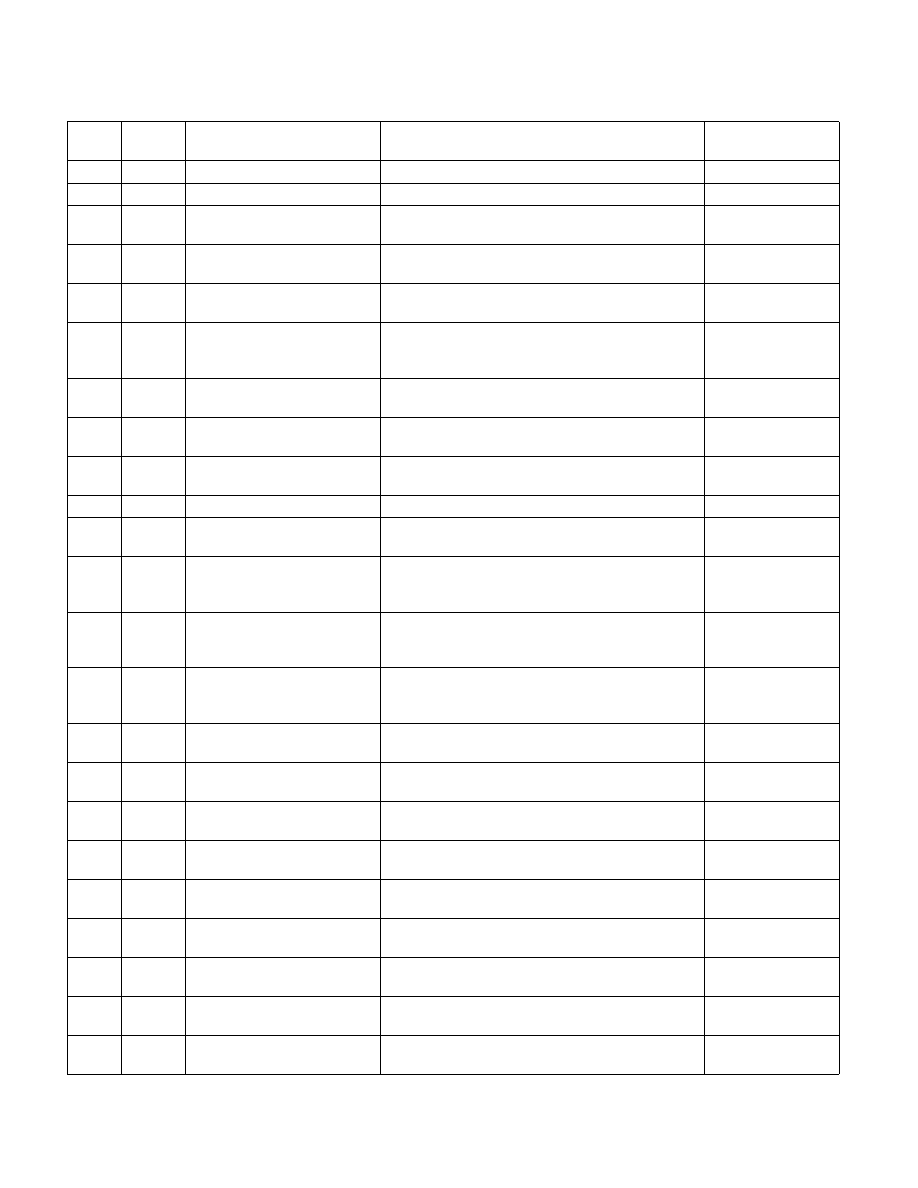

Vol. 3B 19-7

PERFORMANCE-MONITORING EVENTS

79H

30H

IDQ.MS_SWITCHES

Number of switches from DSB or MITE to MS.

EDG

79H

30H

IDQ.MS_CYCLES

Cycles MS is delivered at least one uops.

CMSK1

80H

04H

ICACHE_16B.IFDATA_STALL

Cycles where a code fetch is stalled due to L1

instruction cache miss.

80H

04H

ICACHE_64B.IFDATA_STALL

Cycles where a code fetch is stalled due to L1

instruction cache tag miss.

83H

01H

ICACHE_64B.IFTAG_HIT

Instruction fetch tag lookups that hit in the instruction

cache (L1I). Counts at 64-byte cache-line granularity.

83H

02H

ICACHE_64B.IFTAG_MISS

Instruction fetch tag lookups that miss in the

instruction cache (L1I). Counts at 64-byte cache-line

granularity.

85H

01H

ITLB_MISSES.MISS_CAUSES_A_

WALK

Misses at all ITLB levels that cause page walks.

85H

0EH

ITLB_MISSES.WALK_COMPLETE

D

Counts completed page walks in any TLB level due to

code fetch misses (all page sizes).

85H

10H

ITLB_MISSES.WALK_PENDING

Counts 1 per cycle for each PMH that is busy with a

page walk for an instruction fetch request.

85H

20H

ITLB_MISSES.STLB_HIT

ITLB misses that hit STLB.

87H

01H

ILD_STALL.LCP

Stalls caused by changing prefix length of the

instruction.

9CH

01H

IDQ_UOPS_NOT_DELIVERED.CO

RE

Count issue pipeline slots where no uop was delivered

from the front end to the back end when there is no

back-end stall.

9CH

01H

IDQ_UOPS_NOT_DELIVERED.CYC

LES_0_UOP_DELIV.CORE

Cycles which 4 issue pipeline slots had no uop delivered

from the front end to the back end when there is no

back-end stall.

CMSK4

9CH

01H

IDQ_UOPS_NOT_DELIVERED.CYC

LES_LE_n_UOP_DELIV.CORE

Cycles which “4-n” issue pipeline slots had no uop

delivered from the front end to the back end when

there is no back-end stall.

Set CMSK = 4-n; n = 1,

2, 3

9CH

01H

IDQ_UOPS_NOT_DELIVERED.CYC

LES_FE_WAS_OK

Cycles which front end delivered 4 uops or the RAT was

stalling FE.

CMSK, INV

A1H

01H

UOPS_DISPATCHED_PORT.PORT

_0

Counts the number of cycles in which a uop is

dispatched to port 0.

A1H

02H

UOPS_DISPATCHED_PORT.PORT

_1

Counts the number of cycles in which a uop is

dispatched to port 1.

A1H

04H

UOPS_DISPATCHED_PORT.PORT

_2

Counts the number of cycles in which a uop is

dispatched to port 2.

A1H

08H

UOPS_DISPATCHED_PORT.PORT

_3

Counts the number of cycles in which a uop is

dispatched to port 3.

A1H

10H

UOPS_DISPATCHED_PORT.PORT

_4

Counts the number of cycles in which a uop is

dispatched to port 4.

A1H

20H

UOPS_DISPATCHED_PORT.PORT

_5

Counts the number of cycles in which a uop is

dispatched to port 5.

A1H

40H

UOPS_DISPATCHED_PORT.PORT

_6

Counts the number of cycles in which a uop is

dispatched to port 6.

A1H

80H

UOPS_DISPATCHED_PORT.PORT

_7

Counts the number of cycles in which a uop is

dispatched to port 7.

Table 19-3. Non-Architectural Performance Events of the Processor Core Supported by Skylake Microarchitecture

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment