Vol. 3B 18-111

PERFORMANCE MONITORING

18.21.1 Overview of Performance Monitoring with L3/Caching Bus Controller

The facility for monitoring events consists of a set of dedicated model-specific registers (MSRs). There are eight

event select/counting MSRs that are dedicated to counting events associated with specified microarchitectural

conditions. Programming of these MSRs requires using RDMSR/WRMSR instructions with 64-bit values. In addition,

an MSR MSR_EMON_L3_GL_CTL provides simplified interface to control freezing, resetting, re-enabling operation

of any combination of these event select/counting MSRs.

The eight MSRs dedicated to count occurrences of specific conditions are further divided to count three sub-classes

of microarchitectural conditions:

•

Two MSRs (MSR_EMON_L3_CTR_CTL0 and MSR_EMON_L3_CTR_CTL1) are dedicated to counting GBSQ

events. Up to two GBSQ events can be programmed and counted simultaneously.

•

Two MSRs (MSR_EMON_L3_CTR_CTL2 and MSR_EMON_L3_CTR_CTL3) are dedicated to counting GSNPQ

events. Up to two GBSQ events can be programmed and counted simultaneously.

•

Four MSRs (MSR_EMON_L3_CTR_CTL4, MSR_EMON_L3_CTR_CTL5, MSR_EMON_L3_CTR_CTL6, and

MSR_EMON_L3_CTR_CTL7) are dedicated to counting external bus operations.

The bit fields in each of eight MSRs share the following common characteristics:

•

Bits 63:32 is the event control field that includes an event mask and other bit fields that control counter

operation. The event mask field specifies details of the microarchitectural condition, and its definition differs

across GBSQ, GSNPQ, FSB.

•

Bits 31:0 is the event count field. If the specified condition is met during each relevant clock domain of the

event logic, the matched condition signals the counter logic to increment the associated event count field. The

lower 32-bits of these 8 MSRs at addresses 107CC through 107D3 are treated as 32 bit performance counter

registers.

In Dual-Core Intel Xeon processor 7100 series, the uncore performance counters can be accessed using RDPMC

instruction with the index starting from 18 through 25. The EDX register returns zero when reading these 8 PMCs.

In Intel Xeon processor 7400 series, RDPMC with ECX between 2 and 9 can be used to access the eight uncore

performance counter/control registers.

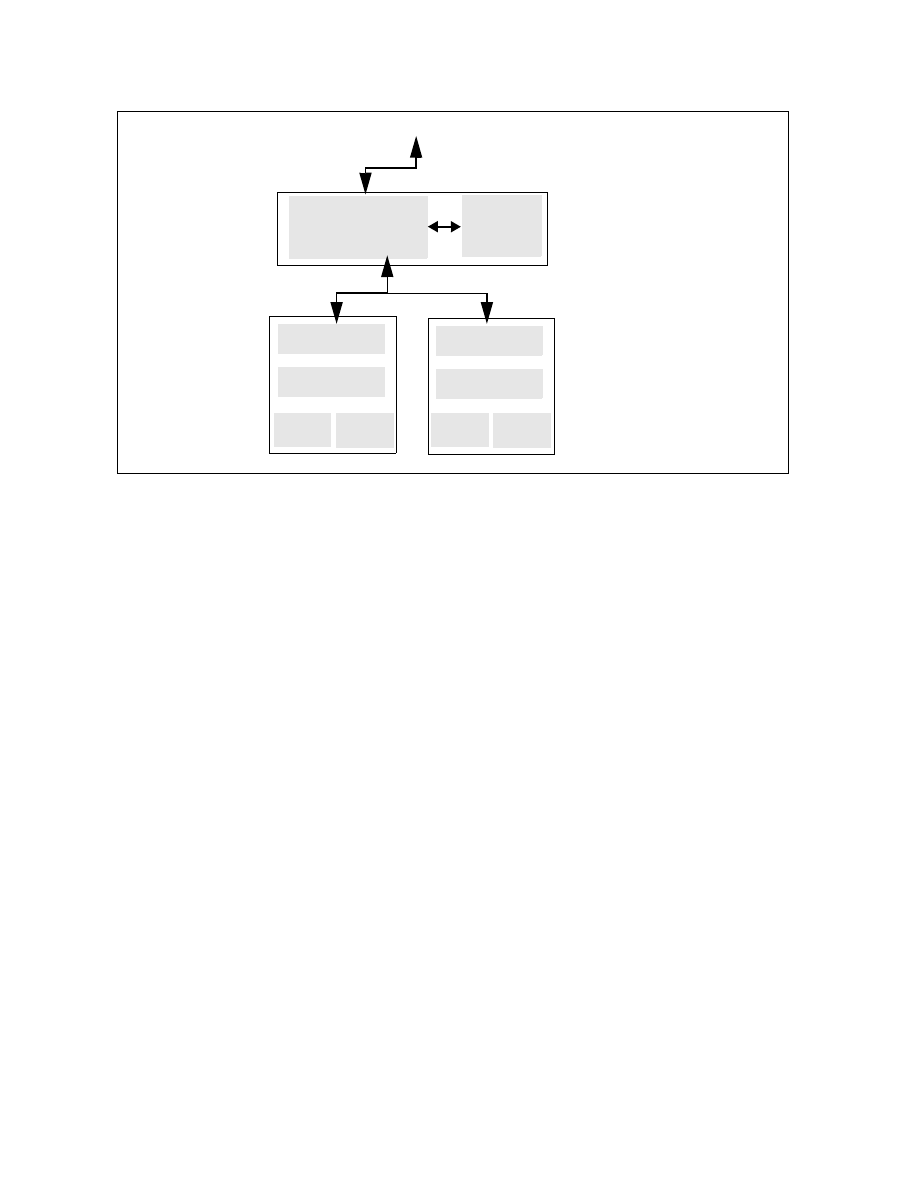

Figure 18-56. Block Diagram of Intel Xeon Processor 7100 Series

SDI interface

Processor core

SDI interface

Processor core

L3

GBSQ, GSNPQ,

GINTQ, ...

FSB

SDI

Logica

l

processor

Logica

l

processor

Logica

l

processor

Logica

l

processor