Vol. 3B 16-27

INTERPRETING MACHINE-CHECK ERROR CODES

Table 16-10 provides information on interpreting additional family 0FH, model specific fields for cache hierarchy

errors. These errors are reported in one of the IA32_MCi_STATUS MSRs. These errors are reported, architecturally,

as compound errors with a general form of 0000 0001 RRRR TTLL in the MCA error code field. See Chapter 15 for

how to interpret the compound error code.

16.10.1 Model-Specific Machine Check Error Codes for Intel Xeon Processor MP 7100 Series

Intel Xeon processor MP 7100 series has 5 register banks which contains information related to Machine Check

Errors. MCi_STATUS[63:0] refers to all 5 register banks. MC0_STATUS[63:0] through MC3_STATUS[63:0] is the

same as on previous generation of Intel Xeon processors within Family 0FH. MC4_STATUS[63:0] is the main error

logging for the processor’s L3 and front side bus errors. It supports the L3 Errors, Bus and Interconnect Errors

Compound Error Codes in the MCA Error Code Field.

19

PIC and FSB data parity

Data Parity detected on either PIC or FSB access

20

Processor Signature =

00000F04H: Invalid PIC

request

All other processors:

Reserved

Processor Signature = 00000F04H. Indicates error due to an invalid PIC

request access was made to PIC space with WB memory):

1 = Invalid PIC request error

0 = No Invalid PIC request error

Reserved

21

Pad state machine

The state machine that tracks P and N data-strobe relative timing has

become unsynchronized or a glitch has been detected.

22

Pad strobe glitch

Data strobe glitch

23

Pad address glitch

Address strobe glitch

Other

Information

24-56 Reserved

Reserved

Status

register

validity

indicators

1

57-63

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

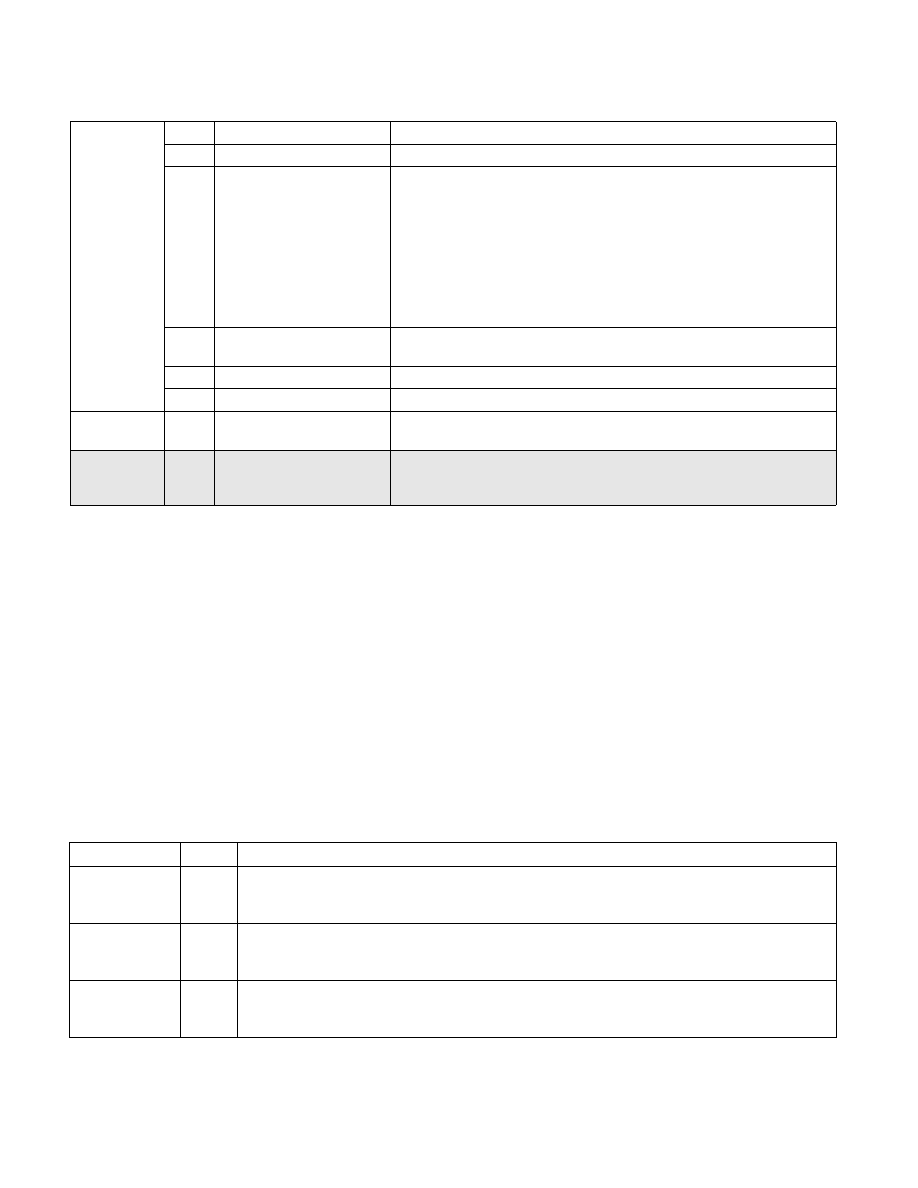

Table 16-32. MCi_STATUS Register Bit Definition

Bit Field Name

Bits

Description

MCA_Error_Code 15:0

Specifies the machine check architecture defined error code for the machine check error condition

detected. The machine check architecture defined error codes are guaranteed to be the same for all

Intel Architecture processors that implement the machine check architecture. See tables below

Model_Specific_E

rror_Code

31:16

Specifies the model specific error code that uniquely identifies the machine check error condition

detected. The model specific error codes may differ among Intel Architecture processors for the same

Machine Check Error condition. See tables below

Other_Info

56:32

The functions of the bits in this field are implementation specific and are not part of the machine check

architecture. Software that is intended to be portable among Intel Architecture processors should not

rely on the values in this field.

Table 16-31. Incremental Decoding Information: Processor Family 0FH Machine Error Codes For Machine Check

Type

Bit No. Bit Function Bit

Description