Vol. 3B 16-25

INTERPRETING MACHINE-CHECK ERROR CODES

16.9.3 Integrated Memory Controller Machine Check Errors

MC error codes associated with integrated memory controllers are reported in the MSRs IA32_MC13_STATUS-

IA32_MC16_STATUS. The supported error codes follow the architectural MCACOD definition type 1MMMCCCC (see

Chapter 15, “Machine-Check Architecture,”).

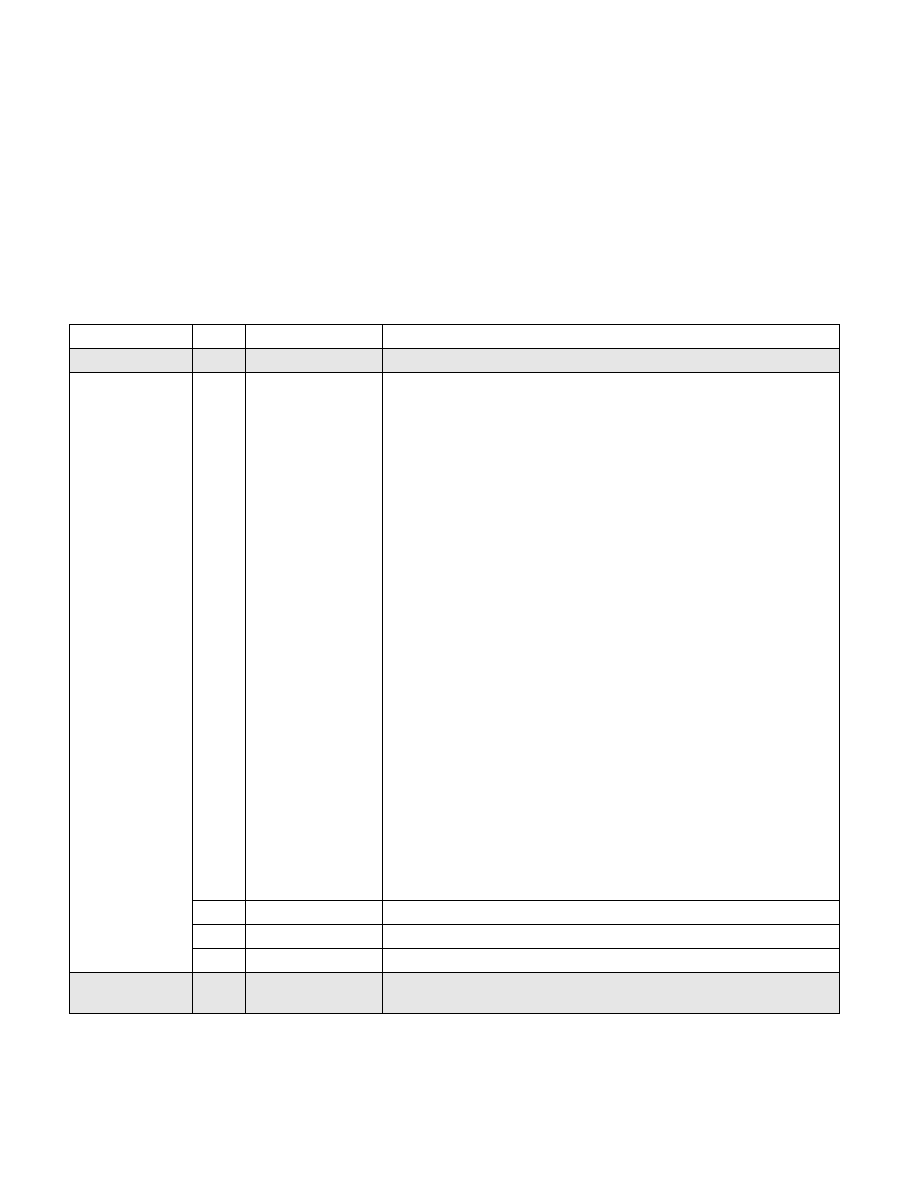

Table 16-29. Intel IMC MC Error Codes for IA32_MCi_STATUS (i= 13-16)

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

Type

Bit No. Bit Function

Bit Description

MCA error codes

1

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

0-15

MCACOD

Memory Controller error format: 0000 0000 1MMM CCCC

Model specific

errors

31:16

Reserved except for

the following

0001H - Address parity error

0002H - HA write data parity error

0004H - HA write byte enable parity error

0008H - Corrected patrol scrub error

0010H - Uncorrected patrol scrub error

0020H - Corrected spare error

0040H - Uncorrected spare error

0080H - Any HA read error

0100H - WDB read parity error

0200H - DDR4 command address parity error

0400H - Uncorrected address parity error

0800H - Unrecognized request type

0801H - Read response to an invalid scoreboard entry

0802H - Unexpected read response

0803H - DDR4 completion to an invalid scoreboard entry

0804H - Completion to an invalid scoreboard entry

0805H - Completion FIFO overflow

0806H - Correctable parity error

0807H - Uncorrectable error

0808H - Interrupt received while outstanding interrupt was not ACKed

0809H - ERID FIFO overflow

080aH - Error on Write credits

080bH - Error on Read credits

080cH - Scheduler error

080dH - Error event

36-32

Other info

MC logs the first error device. This is an encoded 5-bit value of the device.

37

Reserved

Reserved

56-38

See Chapter 15, “Machine-Check Architecture,”

Status register

validity indicators

1

57-63