16-24 Vol. 3B

INTERPRETING MACHINE-CHECK ERROR CODES

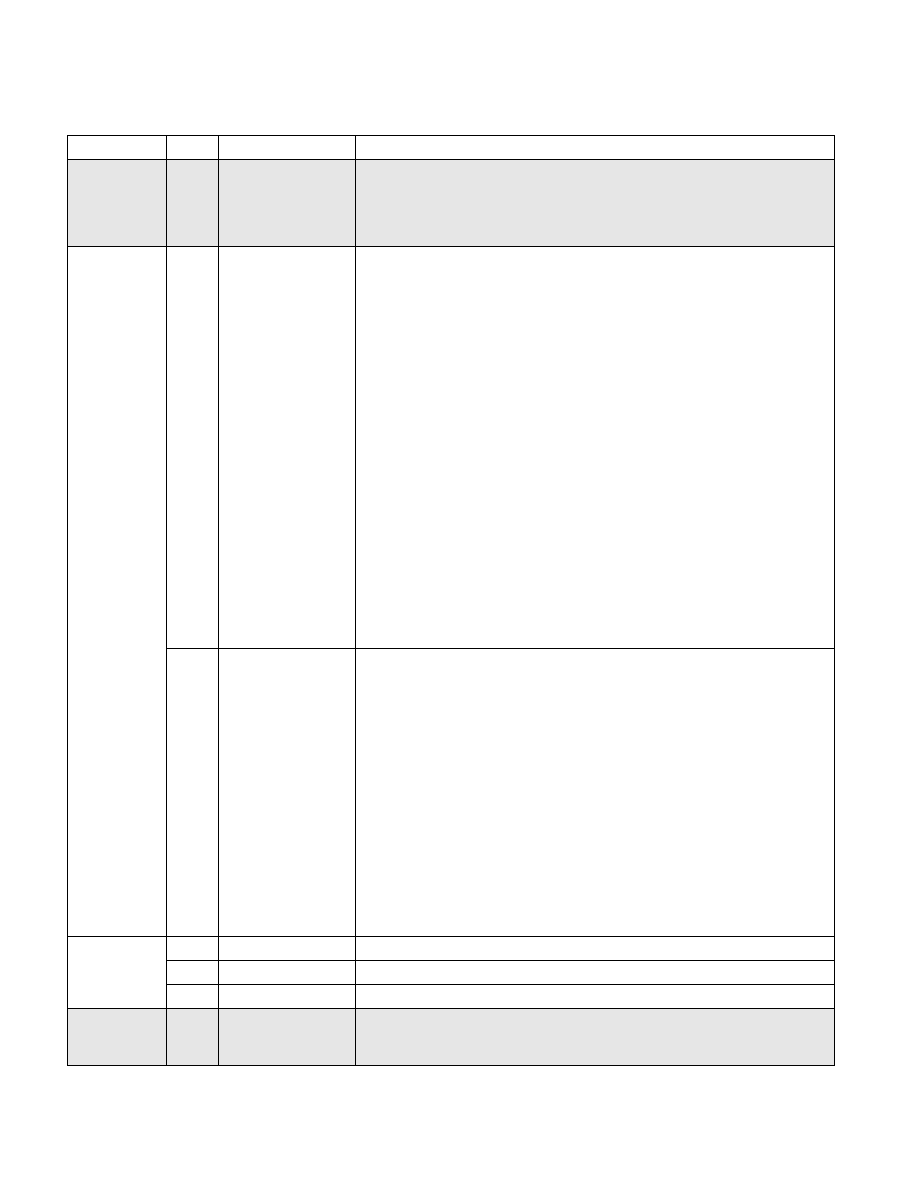

Table 16-28. Interconnect MC Error Codes for IA32_MCi_STATUS, i = 5, 12, 19

Type

Bit No. Bit Function

Bit Description

MCA error

codes

1

0-15

MCACOD

Bus error format: 1PPTRRRRIILL

The two supported compound error codes:

- 0x0C0F - Unsupported/Undefined Packet

- 0x0E0F - For all other corrected and uncorrected errors

Model specific

errors

21-16

MSCOD

The encoding of Uncorrectable (UC) errors are:

00h - UC Phy Initialization Failure.

01h - UC Phy detected drift buffer alarm.

02h - UC Phy detected latency buffer rollover.

10h - UC link layer Rx detected CRC error: unsuccessful LLR entered abort state

11h - UC LL Rx unsupported or undefined packet.

12h - UC LL or Phy control error.

13h - UC LL Rx parameter exchange exception.

1fh - UC LL detected control error from the link-mesh interface

The encoding of correctable (COR) errors are:

20h - COR Phy initialization abort

21h - COR Phy reset

22h - COR Phy lane failure, recovery in x8 width.

23h - COR Phy L0c error corrected without Phy reset

24h - COR Phy L0c error triggering Phy reset

25h - COR Phy L0p exit error corrected with Phy reset

30h - COR LL Rx detected CRC error - successful LLR without Phy re-init.

31h - COR LL Rx detected CRC error - successful LLR with Phy re-init.

All other values are reserved.

31-22

MSCOD_SPARE

The definition below applies to MSCOD 12h (UC LL or Phy Control Errors)

[Bit 22] : Phy Control Error

[Bit 23] : Unexpected Retry.Ack flit

[Bit 24] : Unexpected Retry.Req flit

[Bit 25] : RF parity error

[Bit 26] : Routeback Table error

[Bit 27] : unexpected Tx Protocol flit (EOP, Header or Data)

[Bit 28] : Rx Header-or-Credit BGF credit overflow/underflow

[Bit 29] : Link Layer Reset still in progress when Phy enters L0 (Phy training should

not be enabled until after LL reset is complete as indicated by

KTILCL.LinkLayerReset going back to 0).

[Bit 30] : Link Layer reset initiated while protocol traffic not idle

[Bit 31] : Link Layer Tx Parity Error

37-32

Reserved

Reserved

52-38

Corrected Error Cnt

56-53

Reserved

Reserved

Status register

validity

indicators

1

57-63