16-20 Vol. 3B

INTERPRETING MACHINE-CHECK ERROR CODES

16.7.2 Integrated Memory Controller Machine Check Errors

MC error codes associated with integrated memory controllers are reported in the MSRs IA32_MC9_STATUS-

IA32_MC10_STATUS. The supported error codes follow the architectural MCACOD definition type 1MMMCCCC (see

Chapter 15, “Machine-Check Architecture,”).

MSR_ERROR_CONTROL.[bit 1] can enable additional information logging of the IMC. The additional error informa-

tion logged by the IMC is stored in IA32_MCi_STATUS and IA32_MCi_MISC; (i = 9-10).

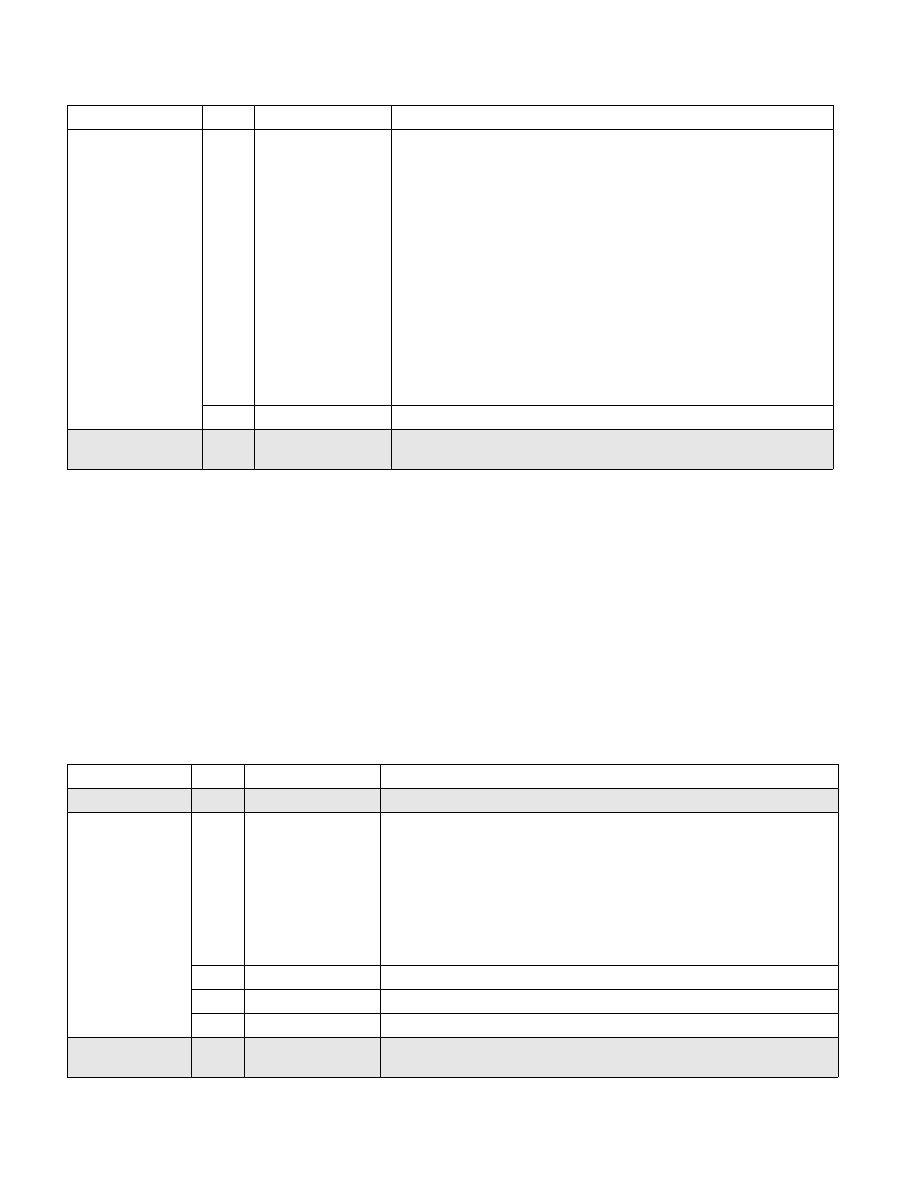

Table 16-25. Intel IMC MC Error Codes for IA32_MCi_STATUS (i= 9-10)

4Bh - MC_PP1_BOOT_VID_TIMEOUT. Timeout setting boot VID for DRAM 0.

4Fh - MC_SVID_COMMAND_ERROR.

52h - MC_FIVR_CATAS_OVERVOL_FAULT.

53h - MC_FIVR_CATAS_OVERCUR_FAULT.

57h - MC_SVID_PKGC_REQUEST_FAILED

58h - MC_SVID_IMON_REQUEST_FAILED

59h - MC_SVID_ALERT_REQUEST_FAILED

62h - MC_INVALID_PKGS_RSP_QPI

64h - MC_INVALID_PKG_STATE_CONFIG

67h - MC_HA_IMC_RW_BLOCK_ACK_TIMEOUT

6Ah - MC_MSGCH_PMREQ_CMP_TIMEOUT

72h - MC_WATCHDG_TIMEOUT_PKGS_MASTER

81h - MC_RECOVERABLE_DIE_THERMAL_TOO_HOT

56-32

Reserved

Reserved

Status register

validity indicators

1

57-63

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

2. The internal error codes may be model-specific.

Type

Bit No. Bit Function

Bit Description

MCA error codes

1

0-15

MCACOD

Memory Controller error format: 0000 0000 1MMM CCCC

Model specific

errors

31:16

Reserved except for

the following

0001H - DDR3 address parity error

0002H - Uncorrected HA write data error

0004H - Uncorrected HA data byte enable error

0008H - Corrected patrol scrub error

0010H - Uncorrected patrol scrub error

0100H - iMC, write data buffer parity errors

0200H - DDR4 command address parity error

36-32

Other info

Reserved

37

Reserved

Reserved

56-38

See Chapter 15, “Machine-Check Architecture,”

Status register

validity indicators

1

57-63

Type

Bit No. Bit Function

Bit Description