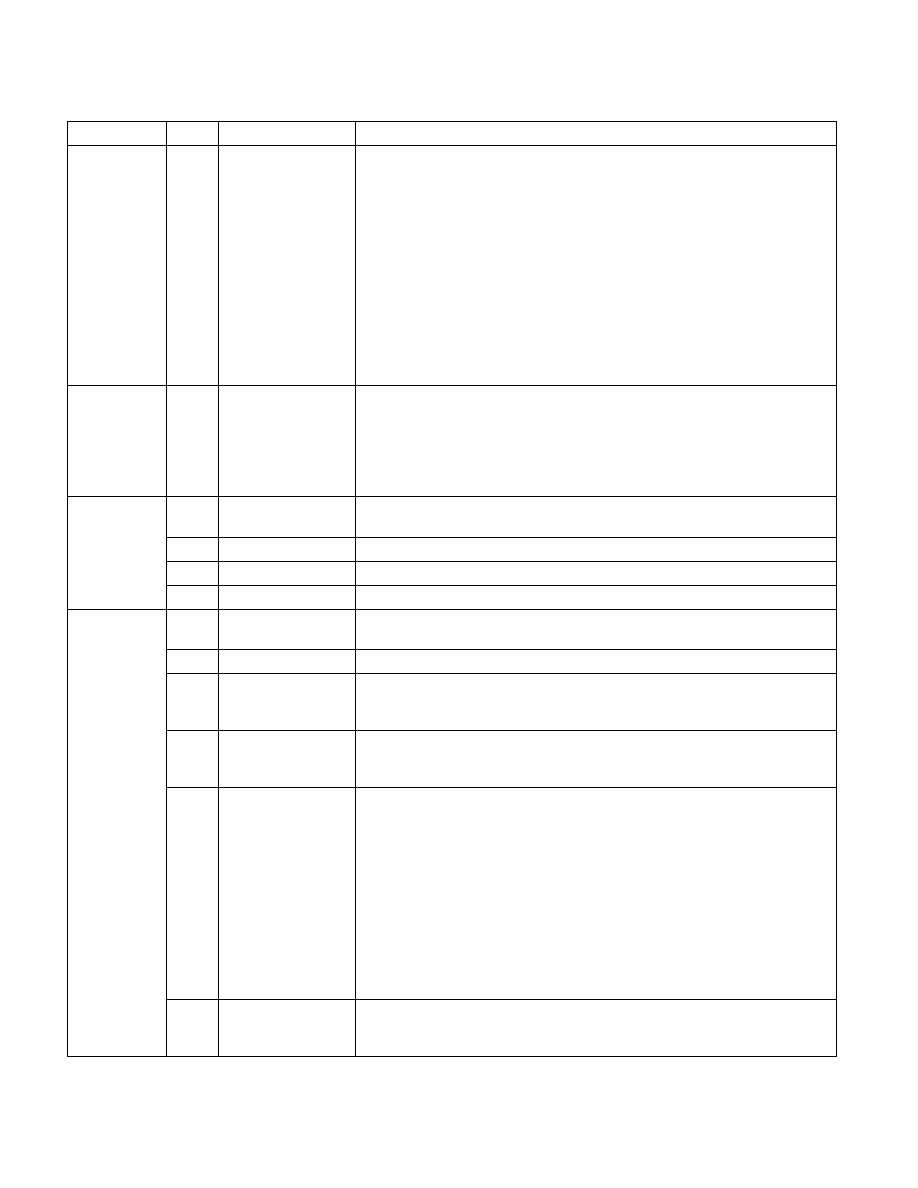

16-2 Vol. 3B

INTERPRETING MACHINE-CHECK ERROR CODES

001101 for BQ_DCU_INTACK_TYPE error

001110 for BQ_DCU_INVALL2_TYPE error

001111 for BQ_DCU_FLUSHL2_TYPE error

010000 for BQ_DCU_PART_RD_TYPE error

010010 for BQ_DCU_PART_WR_TYPE error

010100 for BQ_DCU_SPEC_CYC_TYPE error

011000 for BQ_DCU_IO_RD_TYPE error

011001 for BQ_DCU_IO_WR_TYPE error

011100 for BQ_DCU_LOCK_RD_TYPE error

011110 for BQ_DCU_SPLOCK_RD_TYPE error

011101 for BQ_DCU_LOCK_WR_TYPE error

Model specific

errors

27-25 Bus queue error type 000 for BQ_ERR_HARD_TYPE error

001 for BQ_ERR_DOUBLE_TYPE error

010 for BQ_ERR_AERR2_TYPE error

100 for BQ_ERR_SINGLE_TYPE error

101 for BQ_ERR_AERR1_TYPE error

Model specific

errors

28

FRC error

1 if FRC error active

29

BERR

1 if BERR is driven

30

Internal BINIT

1 if BINIT driven for this processor

31 Reserved

Reserved

Other

information

32-34 Reserved

Reserved

35

External BINIT

1 if BINIT is received from external bus.

36

Response parity error This bit is asserted in IA32_MCi_STATUS if this component has received a parity

error on the RS[2:0]# pins for a response transaction. The RS signals are checked

by the RSP# external pin.

37

Bus BINIT

This bit is asserted in IA32_MCi_STATUS if this component has received a hard

error response on a split transaction one access that has needed to be split across

the 64-bit external bus interface into two accesses).

38

Timeout BINIT

This bit is asserted in IA32_MCi_STATUS if this component has experienced a ROB

time-out, which indicates that no micro-instruction has been retired for a

predetermined period of time.

A ROB time-out occurs when the 15-bit ROB time-out counter carries a 1 out of its

high order bit.

2

The timer is cleared when a micro-instruction retires, an exception

is detected by the core processor, RESET is asserted, or when a ROB BINIT occurs.

The ROB time-out counter is prescaled by the 8-bit PIC timer which is a divide by

128 of the bus clock the bus clock is 1:2, 1:3, 1:4 of the core clock). When a carry

out of the 8-bit PIC timer occurs, the ROB counter counts up by one. While this bit

is asserted, it cannot be overwritten by another error.

39-41

Reserved

Reserved

42

Hard error

This bit is asserted in IA32_MCi_STATUS if this component has initiated a bus

transactions which has received a hard error response. While this bit is asserted, it

cannot be overwritten.

Table 16-2. Incremental Decoding Information: Processor Family 06H Machine Error Codes For Machine Check

Type

Bit No. Bit Function

Bit Description