15-12 Vol. 3B

MACHINE-CHECK ARCHITECTURE

When a machine-check error is detected on a Pentium 4 or Intel Xeon processor, the processor saves the state of

the general-purpose registers, the R/EFLAGS register, and the R/EIP in these extended machine-check state MSRs.

This information can be used by a debugger to analyze the error.

These registers are read/write to zero registers. This means software can read them; but if software writes to

them, only all zeros is allowed. If software attempts to write a non-zero value into one of these registers, a general-

protection (#GP) exception is generated. These registers are cleared on a hardware reset (power-up or RESET),

but maintain their contents following a soft reset (INIT reset).

15.3.3

Mapping of the Pentium

Processor Machine-Check Errors

to the Machine-Check Architecture

The Pentium processor reports machine-check errors using two registers: P5_MC_TYPE and P5_MC_ADDR. The

Pentium 4, Intel Xeon, Intel Atom, and P6 family processors map these registers to the IA32_MCi_STATUS and

IA32_MCi_ADDR in the error-reporting register bank. This bank reports on the same type of external bus errors

reported in P5_MC_TYPE and P5_MC_ADDR.

The information in these registers can then be accessed in two ways:

•

By reading the IA32_MCi_STATUS and IA32_MCi_ADDR registers as part of a general machine-check exception

handler written for Pentium 4, Intel Atom and P6 family processors.

•

By reading the P5_MC_TYPE and P5_MC_ADDR registers using the RDMSR instruction.

The second capability permits a machine-check exception handler written to run on a Pentium processor to be run

on a Pentium 4, Intel Xeon, Intel Atom, or P6 family processor. There is a limitation in that information returned by

the Pentium 4, Intel Xeon, Intel Atom, and P6 family processors is encoded differently than information returned

by the Pentium processor. To run a Pentium processor machine-check exception handler on a Pentium 4, Intel

Xeon, Intel Atom, or P6 family processor; the handler must be written to interpret P5_MC_TYPE encodings

correctly.

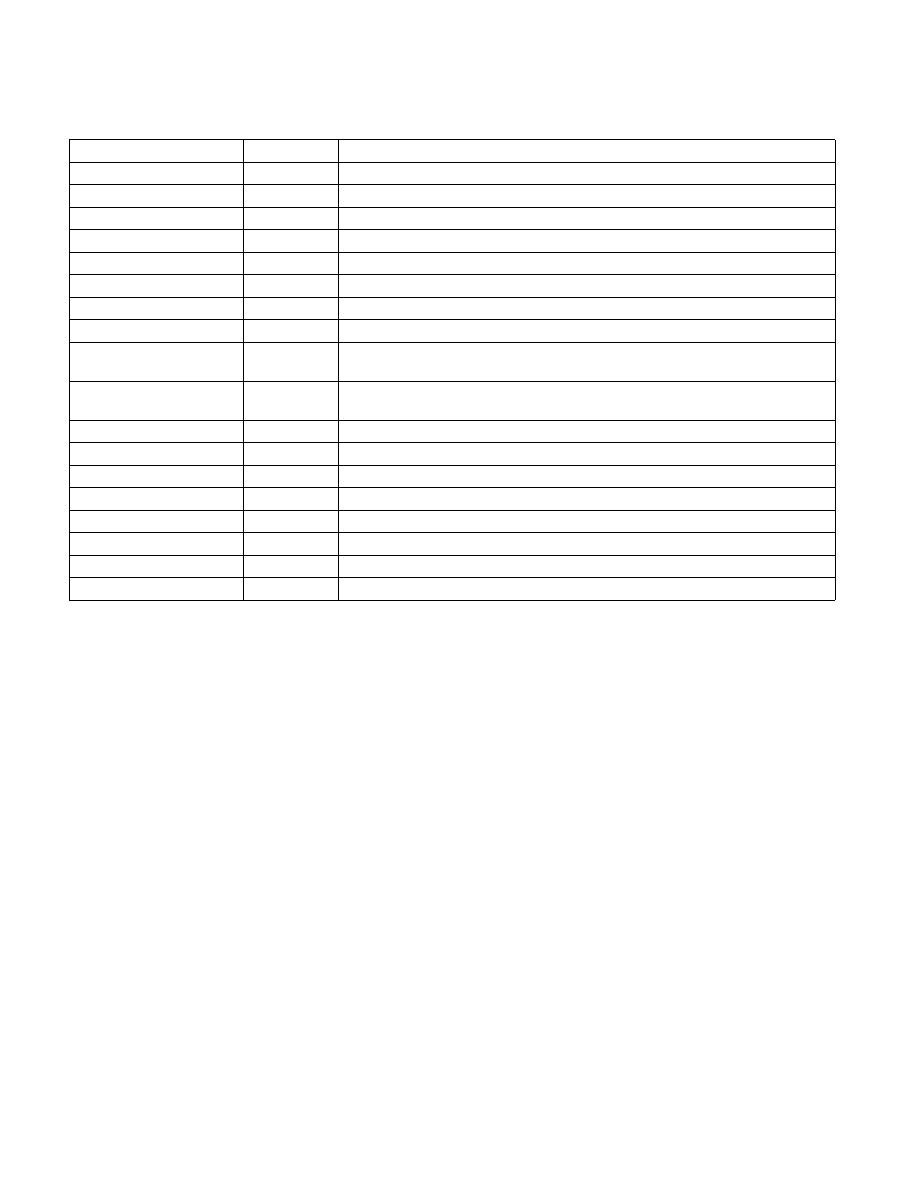

IA32_MCG_RCX

182H

Contains state of the RCX register at the time of the machine-check error.

IA32_MCG_RDX

183H

Contains state of the RDX register at the time of the machine-check error.

IA32_MCG_RSI

184H

Contains state of the RSI register at the time of the machine-check error.

IA32_MCG_RDI

185H

Contains state of the RDI register at the time of the machine-check error.

IA32_MCG_RBP

186H

Contains state of the RBP register at the time of the machine-check error.

IA32_MCG_RSP

187H

Contains state of the RSP register at the time of the machine-check error.

IA32_MCG_RFLAGS

188H

Contains state of the RFLAGS register at the time of the machine-check error.

IA32_MCG_RIP

189H

Contains state of the RIP register at the time of the machine-check error.

IA32_MCG_MISC

18AH

When set, indicates that a page assist or page fault occurred during DS normal

operation.

IA32_MCG_

RSERVED[1:5]

18BH-

18FH

These registers, if present, are reserved.

IA32_MCG_R8

190H

Contains state of the R8 register at the time of the machine-check error.

IA32_MCG_R9

191H

Contains state of the R9 register at the time of the machine-check error.

IA32_MCG_R10

192H

Contains state of the R10 register at the time of the machine-check error.

IA32_MCG_R11

193H

Contains state of the R11 register at the time of the machine-check error.

IA32_MCG_R12

194H

Contains state of the R12 register at the time of the machine-check error.

IA32_MCG_R13

195H

Contains state of the R13 register at the time of the machine-check error.

IA32_MCG_R14

196H

Contains state of the R14 register at the time of the machine-check error.

IA32_MCG_R15

197H

Contains state of the R15 register at the time of the machine-check error.

Table 15-5. Extended Machine Check State MSRs

In Processors With Support For Intel 64 Architecture (Contd.)

MSR

Address

Description