14-6 Vol. 3B

POWER AND THERMAL MANAGEMENT

When HWP is enabled, the processor autonomously selects performance states as deemed appropriate for the

applied workload and with consideration of constraining hints that are programmed by the OS. These OS-provided

hints include minimum and maximum performance limits, preference towards energy efficiency or performance,

and the specification of a relevant workload history observation time window. The means for the OS to override

HWP's autonomous selection of performance state with a specific desired performance target is also provided,

however, the effective frequency delivered is subject to the result of energy efficiency and performance optimiza-

tions.

14.4.1

HWP Programming Interfaces

The programming interfaces provided by HWP include the following:

•

The CPUID instruction allows software to discover the presence of HWP support in an Intel processor. Specifi-

cally, execute CPUID instruction with EAX=06H as input will return 5 bit flags covering the following aspects in

bits 7 through 11 of CPUID.06H:EAX:

— Availability of HWP baseline resource and capability, CPUID.06H:EAX[bit 7]: If this bit is set, HWP provides

several new architectural MSRs: IA32_PM_ENABLE, IA32_HWP_CAPABILITIES, IA32_HWP_REQUEST,

IA32_HWP_STATUS.

— Availability of HWP Notification upon dynamic Guaranteed Performance change, CPUID.06H:EAX[bit 8]: If

this bit is set, HWP provides IA32_HWP_INTERRUPT MSR to enable interrupt generation due to dynamic

Performance changes and excursions.

— Availability of HWP Activity window control, CPUID.06H:EAX[bit 9]: If this bit is set, HWP allows software to

program activity window in the IA32_HWP_REQUEST MSR.

— Availability of HWP energy/performance preference control, CPUID.06H:EAX[bit 10]: If this bit is set, HWP

allows software to set an energy/performance preference hint in the IA32_HWP_REQUEST MSR.

— Availability of HWP package level control, CPUID.06H:EAX[bit 11]:If this bit is set, HWP provides the

IA32_HWP_REQUEST_PKG MSR to convey OS Power Management’s control hints for all logical processors

in the physical package.

•

Additionally, HWP may provide a non-architectural MSR, MSR_PPERF, which provides a quantitative metric to

software of hardware’s view of workload scalability. This hardware’s view of workload scalability is implemen-

tation specific.

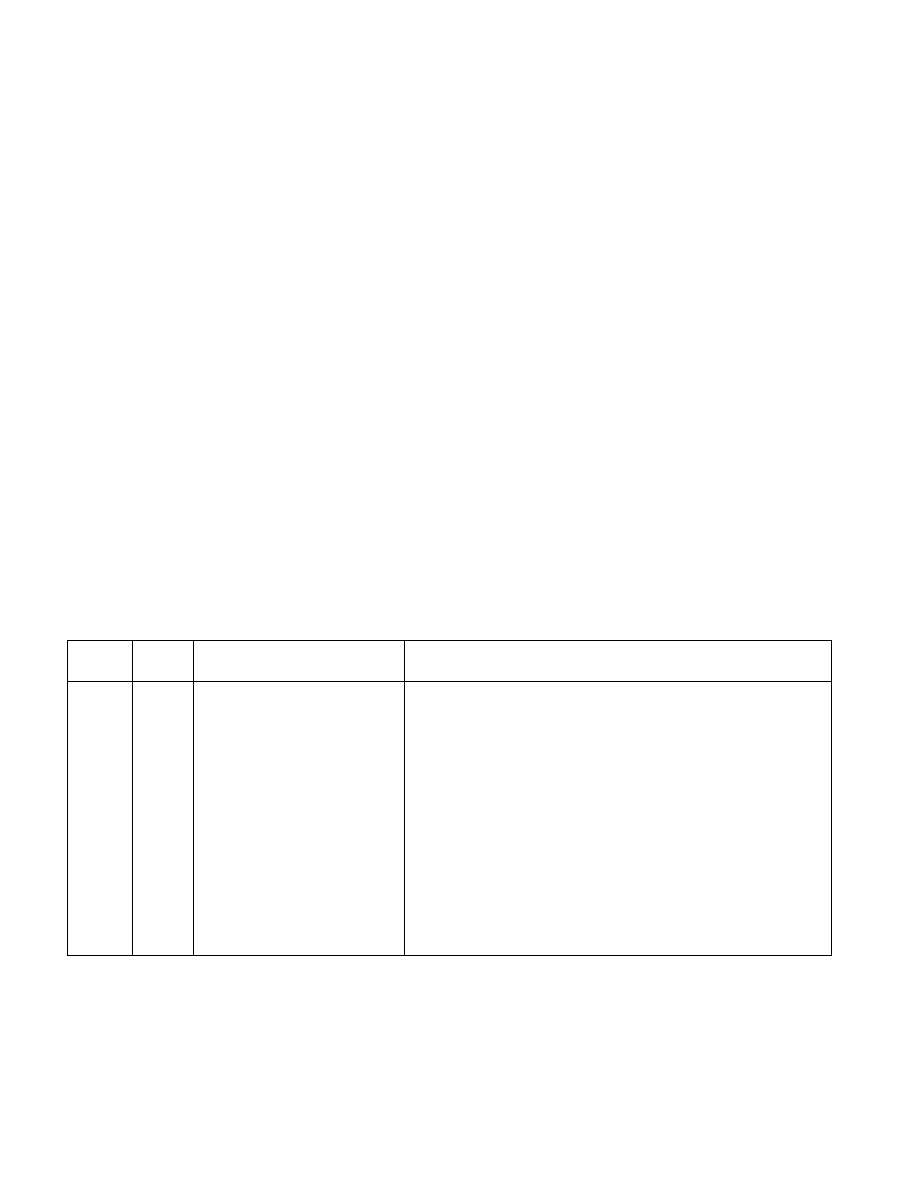

Table 14-1. Architectural and Non-Architectural MSRs Related to HWP

Address Archite

ctural

Register Name

Description

770H

Y

IA32_PM_ENABLE

Enable/Disable HWP.

771H

Y

IA32_HWP_CAPABILITIES

Enumerates the HWP performance range (static and dynamic).

772H

Y

IA32_HWP_REQUEST_PKG

Conveys OSPM's control hints (Min, Max, Activity Window, Energy

Performance Preference, Desired) for all logical processor in the physical

package.

773H

Y

IA32_HWP_INTERRUPT

Controls HWP native interrupt generation (Guaranteed Performance

changes, excursions).

774H

Y

IA32_HWP_REQUEST

Conveys OSPM's control hints (Min, Max, Activity Window, Energy

Performance Preference, Desired) for a single logical processor.

777H

Y

IA32_HWP_STATUS

Status bits indicating changes to Guaranteed Performance and

excursions to Minimum Performance.

19CH

Y

IA32_THERM_STATUS[bits 15:12] Conveys reasons for performance excursions

64EH

N

MSR_PPERF

Productive Performance Count.