13-8 Vol. 3A

SYSTEM PROGRAMMING FOR INSTRUCTION SET EXTENSIONS AND PROCESSOR EXTENDED STATES

ŌĆó

Control register enhancement and dedicated register for enabling each processor extended state. See Section

13.3 of the Intel┬« 64 and IA-32 Architectures Software DeveloperŌĆÖs Manual, Volume 1.

ŌĆó

Instructions to save state to and restore state from the XSAVE area. See Section 13.7 through Section 13.9 of

the Intel┬« 64 and IA-32 Architectures Software DeveloperŌĆÖs Manual, Volume 1.

Operating systems can utilize XSAVE feature set to manage both FP/SSE state and processor extended states.

CPUID leaf 0DH enumerates XSAVE feature set related information. The following guidelines provide the steps an

operating system needs to take to support legacy FP/SSE states and processor extended states.

1. Check that the processor supports the XSAVE feature set

2. Determine the set of XSAVE managed features that the operating system intends to enable and calculate the

size of the buffer needed to save/restore the states during context switch and other flows

3. Enable use of XSAVE feature set and XSAVE managed features

4. Provide an initialization for the XSAVE managed feature state components

5. Provide (if necessary) required exception handlers for exceptions generated each of the XSAVE managed

features.

13.5.1

Checking the Support for XSAVE Feature Set

Support for XSAVE Feature set is enumerated in CPUID.1.ECX.XSAVE[bit 26]. Enumeration of this bit indicates that

the processor supports XSAVE/XRSTOR instructions to manage state and XSETBV/XGETBV on XCR0 to enable and

get enabled states. An operating system needs to enable XSAVE feature set as described later.

Additionally CPUID.(EAX=0DH, ECX=1).EAX enumerates additional XSAVE sub features such as optimized save,

compaction and supervisor state support. The following table summarizes XSAVE sub features. Once an operating

system enables XSAVE feature set, all the sub-features enumerated are also available. There is no need to enable

each additional sub feature.

13.5.2

Determining the XSAVE Managed Feature States And The Required Buffer Size

Each XSAVE managed feature has one or more state components associated with it. An operating system policy

needs to determine the XSAVE managed features to support and determine the corresponding state components

to enable. When determining the XSAVE managed features to support, operating system needs to take into account

the dependencies between them (e.g. AVX feature depends on SSE feature). Similarly, when a XSAVE managed

feature has more than one state component, all of them need to be enabled. Each logical processor enumerates

supported XSAVE state components in CPUID.(EAX=0DH, ECX=0).EDX:EAX. An operating system may enable all

or a subset of the state components enumerated by the processor based on the OS policy.

The size of the memory buffer needed to save enabled XSAVE state components depends on whether the OS opts-

in to use compacted format or not. Section 13.4.3 of the Intel┬« 64 and IA-32 Architectures Software DeveloperŌĆÖs

Manual, Volume 1 describes the layout of the extended region of the XSAVE area.

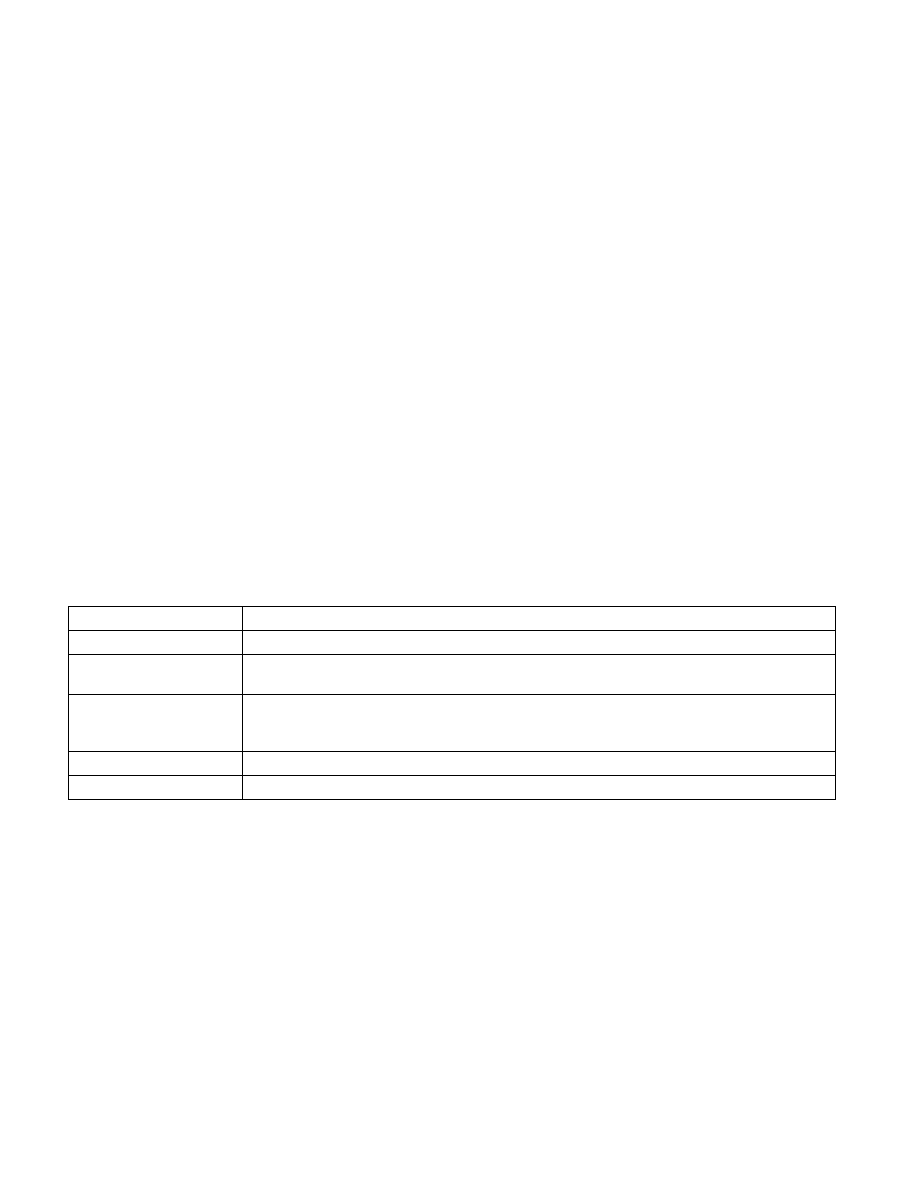

Table 13-3. CPUID.(EAX=0DH, ECX=1) EAX Bit Assignment

EAX Bit Position

Meaning

0

If set, indicates availability of the XSAVEOPT instruction.

1

If set, indicates availability of the XSAVEC instruction and the corresponding compaction enhancements

to the legacy XRSTOR instruction.

2

If set, indicates support for execution of XGETBV with ECX=1. This execution returns the state-compo-

nent bitmap XINUSE. If XINUSE[i] = 0, state component i is in its initial configuration. Execution of

XSETBV with ECX=1 causes a #GP.

3

If set, indicates support for XSAVES/XRSTORS and IA32_XSS MSR

31:4

Reserved