Vol. 3A 9-3

PROCESSOR MANAGEMENT AND INITIALIZATION

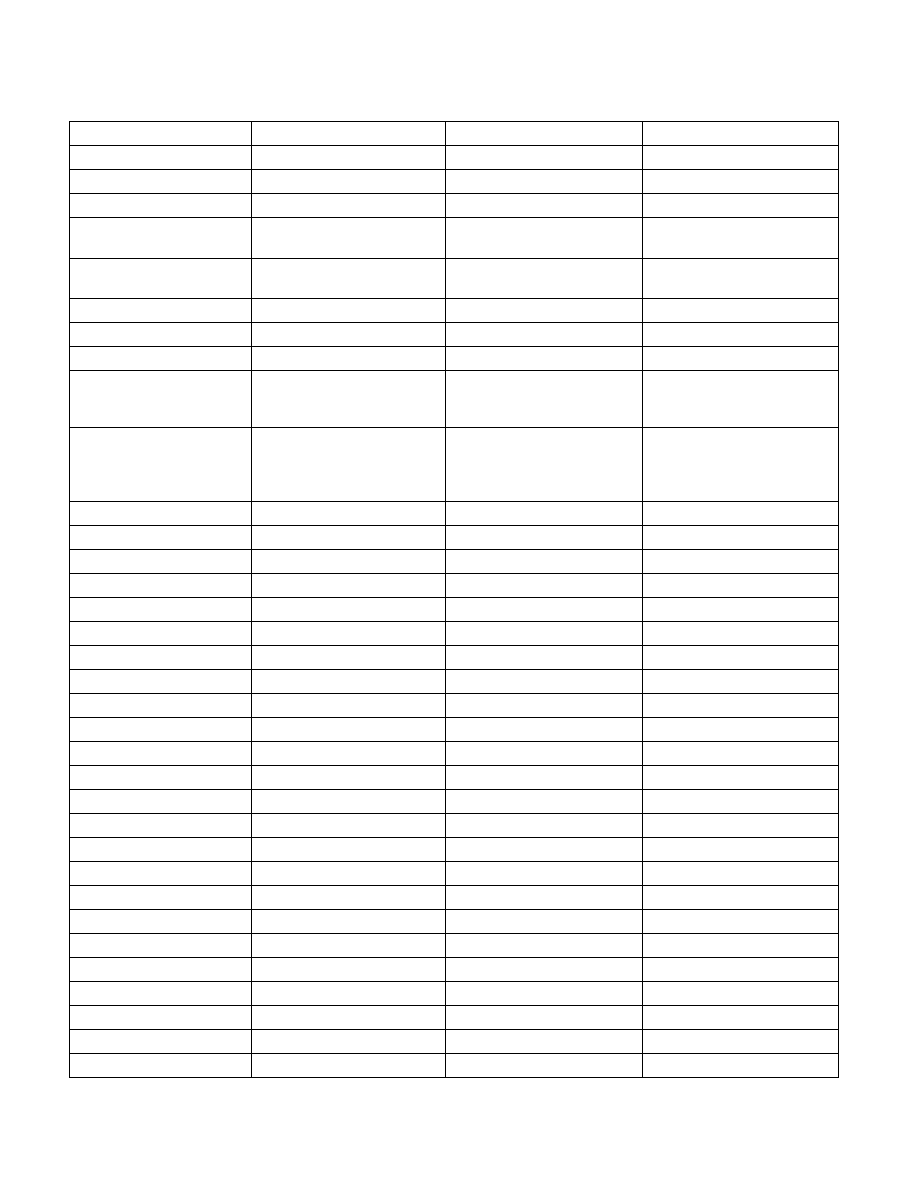

x87 FPU Control Word

5

0040H

0040H

FINIT/FNINIT: 037FH

x87 FPU Status Word

5

0000H

0000H

FINIT/FNINIT: 0000H

x87 FPU Tag Word

5

5555H

5555H

FINIT/FNINIT: FFFFH

x87 FPU Data Operand and

CS Seg. Selectors

5

0000H

0000H

FINIT/FNINIT: 0000H

x87 FPU Data Operand and

Inst. Pointers

5

00000000H

00000000H

FINIT/FNINIT: 00000000H

MM0 through MM7

5

0000000000000000H

0000000000000000H

INIT or FINIT/FNINIT: Unchanged

XMM0 through XMM7

0H

0H

Unchanged

MXCSR

1F80H

1F80H

Unchanged

GDTR, IDTR

Base = 00000000H

Limit = FFFFH

AR = Present, R/W

Base = 00000000H

Limit = FFFFH

AR = Present, R/W

Base = 00000000H

Limit = FFFFH

AR = Present, R/W

LDTR, Task Register

Selector = 0000H

Base = 00000000H

Limit = FFFFH

AR = Present, R/W

Selector = 0000H

Base = 00000000H

Limit = FFFFH

AR = Present, R/W

Selector = 0000H

Base = 00000000H

Limit = FFFFH

AR = Present, R/W

DR0, DR1, DR2, DR3

00000000H

00000000H

00000000H

DR6

FFFF0FF0H

FFFF0FF0H

FFFF0FF0H

DR7

00000400H

00000400H

00000400H

R8-R15

0000000000000000H

0000000000000000H

0000000000000000H

XMM8-XMM15

0H

0H

Unchanged

XCR0

3H

3H

Unchanged

IA32_XSS

0H

0H

0H

YMM_H[255:128]

0H

0H

Unchanged

BNDCFGU

0H

0H

0H

BND0-BND3

0H

0H

0H

IA32_BNDCFGS

0H

0H

0H

OPMASK 0H

0H

Unchanged

ZMM_H[511:256]

0H

0H

Unchanged

ZMMHi16[511:0]

0H

0H

Unchanged

PKRU

0H

0H

Unchanged

Intel Processor Trace MSRs

0H

0H

W

Unchanged

Time-Stamp Counter

0H

0H

W

Unchanged

IA32_TSC_AUX

0H

0H

Unchanged

IA32_TSC_ADJUST

0H

0H

Unchanged

IA32_TSC_DEADLINE

0H

0H

Unchanged

IA32_SYSENTER_CS/ESP/EIP

0H

0H

Unchanged

IA32_EFER

0000000000000000H

0000000000000000H

0000000000000000H

IA32_STAR/LSTAR

0H

0H

Unchanged

IA32_FS_BASE/GS_BASE

0H

0H

0H

Table 9-1. IA-32 and Intel 64 Processor States Following Power-up, Reset, or INIT (Contd.)

Register

Power up

Reset

INIT