8-10 Vol. 3A

MULTIPLE-PROCESSOR MANAGEMENT

At each processor, the load and the store are to different locations and hence may be reordered. Any interleaving

of the operations is thus allowed. One such interleaving has the two loads occurring before the two stores. This

would result in each load returning value 0.

The fact that a load may not be reordered with an earlier store to the same location is illustrated by the following

example:

The Intel-64 memory-ordering model does not allow the load to be reordered with the earlier store because the

accesses are to the same location. Therefore, r1 = 1 must hold.

8.2.3.5

Intra-Processor Forwarding Is Allowed

The memory-ordering model allows concurrent stores by two processors to be seen in different orders by those two

processors; specifically, each processor may perceive its own store occurring before that of the other. This is illus-

trated by the following example:

The memory-ordering model imposes no constraints on the order in which the two stores appear to execute by the

two processors. This fact allows processor 0 to see its store before seeing processor 1's, while processor 1 sees its

store before seeing processor 0's. (Each processor is self consistent.) This allows r2 = 0 and r4 = 0.

In practice, the reordering in this example can arise as a result of store-buffer forwarding. While a store is tempo-

rarily held in a processor's store buffer, it can satisfy the processor's own loads but is not visible to (and cannot

satisfy) loads by other processors.

8.2.3.6

Stores Are Transitively Visible

The memory-ordering model ensures transitive visibility of stores; stores that are causally related appear to all

processors to occur in an order consistent with the causality relation. This is illustrated by the following example:

Assume that r1 = 1 and r2 = 1.

•

Because r1 = 1, processor 0’s store occurs before processor 1’s load.

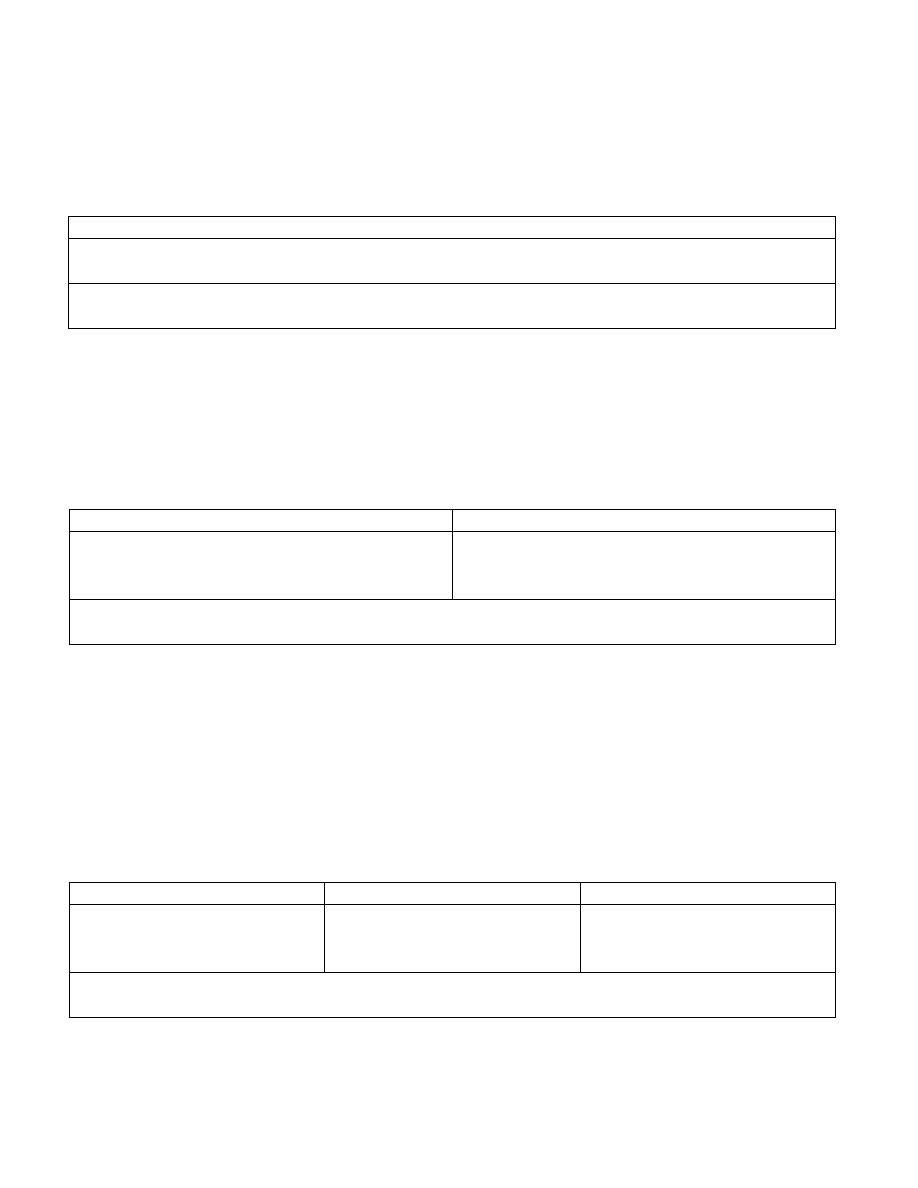

Example 8-4. Loads Are not Reordered with Older Stores to the Same Location

Processor 0

mov [ _x], 1

mov r1, [ _x]

Initially x = 0

r1 = 0 is not allowed

Example 8-5. Intra-Processor Forwarding is Allowed

Processor 0

Processor 1

mov [ _x], 1

mov [ _y], 1

mov r1, [ _x]

mov r3, [ _y]

mov r2, [ _y]

mov r4, [ _x]

Initially x = y = 0

r2 = 0 and r4 = 0 is allowed

Example 8-6. Stores Are Transitively Visible

Processor 0

Processor 1

Processor 2

mov [ _x], 1

mov r1, [ _x]

mov [ _y], 1

mov r2, [ _y]

mov r3, [_x]

Initially x = y = 0

r1 = 1, r2 = 1, r3 = 0 is not allowed