7-2 Vol. 3A

TASK MANAGEMENT

7.1.2 Task

State

The following items define the state of the currently executing task:

•

The task’s current execution space, defined by the segment selectors in the segment registers (CS, DS, SS, ES,

FS, and GS).

•

The state of the general-purpose registers.

•

The state of the EFLAGS register.

•

The state of the EIP register.

•

The state of control register CR3.

•

The state of the task register.

•

The state of the LDTR register.

•

The I/O map base address and I/O map (contained in the TSS).

•

Stack pointers to the privilege 0, 1, and 2 stacks (contained in the TSS).

•

Link to previously executed task (contained in the TSS).

Prior to dispatching a task, all of these items are contained in the task’s TSS, except the state of the task register.

Also, the complete contents of the LDTR register are not contained in the TSS, only the segment selector for the

LDT.

7.1.3 Executing

a

Task

Software or the processor can dispatch a task for execution in one of the following ways:

•

A explicit call to a task with the CALL instruction.

•

A explicit jump to a task with the JMP instruction.

•

An implicit call (by the processor) to an interrupt-handler task.

•

An implicit call to an exception-handler task.

•

A return (initiated with an IRET instruction) when the NT flag in the EFLAGS register is set.

All of these methods for dispatching a task identify the task to be dispatched with a segment selector that points to

a task gate or the TSS for the task. When dispatching a task with a CALL or JMP instruction, the selector in the

instruction may select the TSS directly or a task gate that holds the selector for the TSS. When dispatching a task

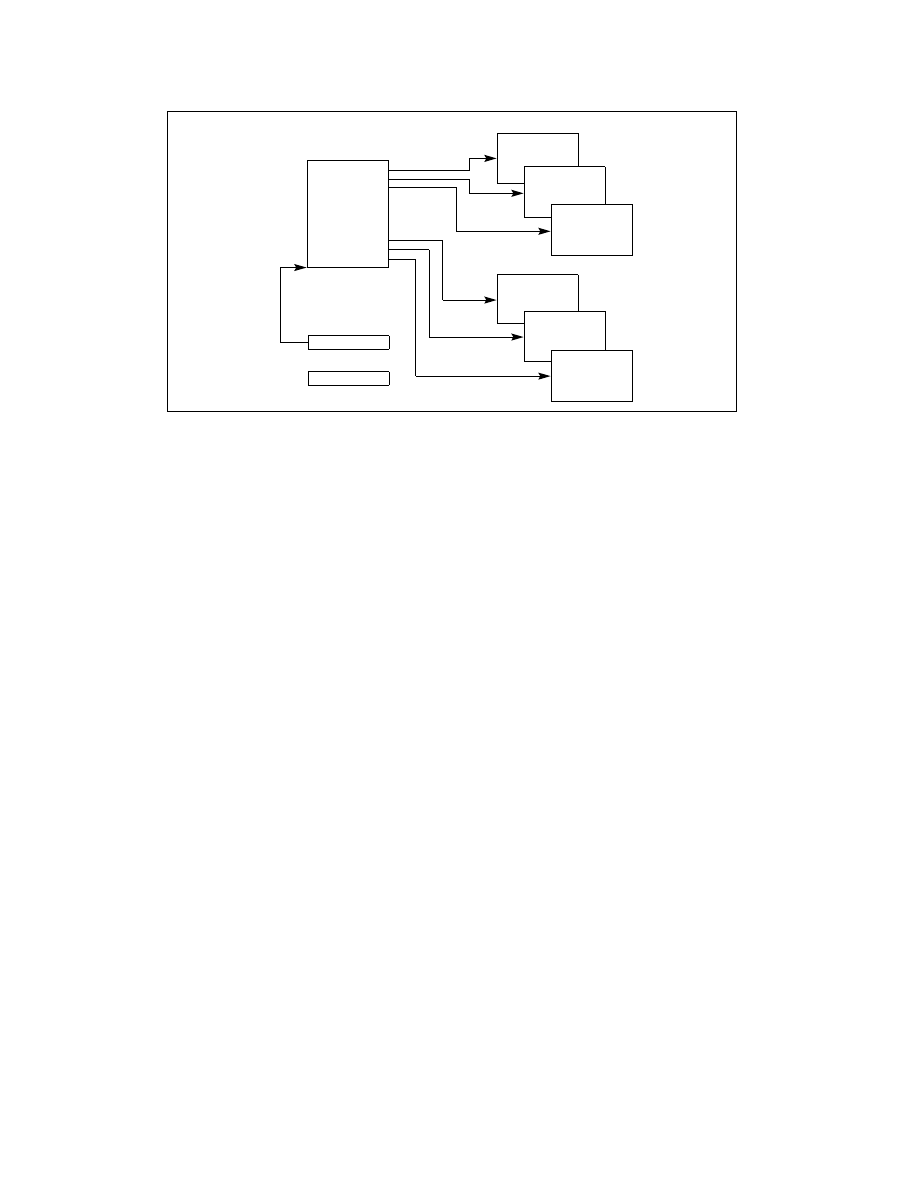

Figure 7-1. Structure of a Task

Code

Segment

Stack

Segment

(Current Priv.

Data

Segment

Stack Seg.

Priv. Level 0

Stack Seg.

Priv. Level 1

Stack

Segment

(Priv. Level 2)

Task-State

Segment

(TSS)

Task Register

CR3

Level)