Vol. 3A 6-49

INTERRUPT AND EXCEPTION HANDLING

Exception Error Code

None.

Saved Instruction Pointer

The saved contents of CS and EIP registers point to the SSE/SSE2/SSE3 instruction that was executed when the

SIMD floating-point exception was generated. This is the faulting instruction in which the error condition was

detected.

Program State Change

A program-state change does not accompany a SIMD floating-point exception because the handling of the excep-

tion is immediate unless the particular exception is masked. The available state information is often sufficient to

allow recovery from the error and re-execution of the faulting instruction if needed.

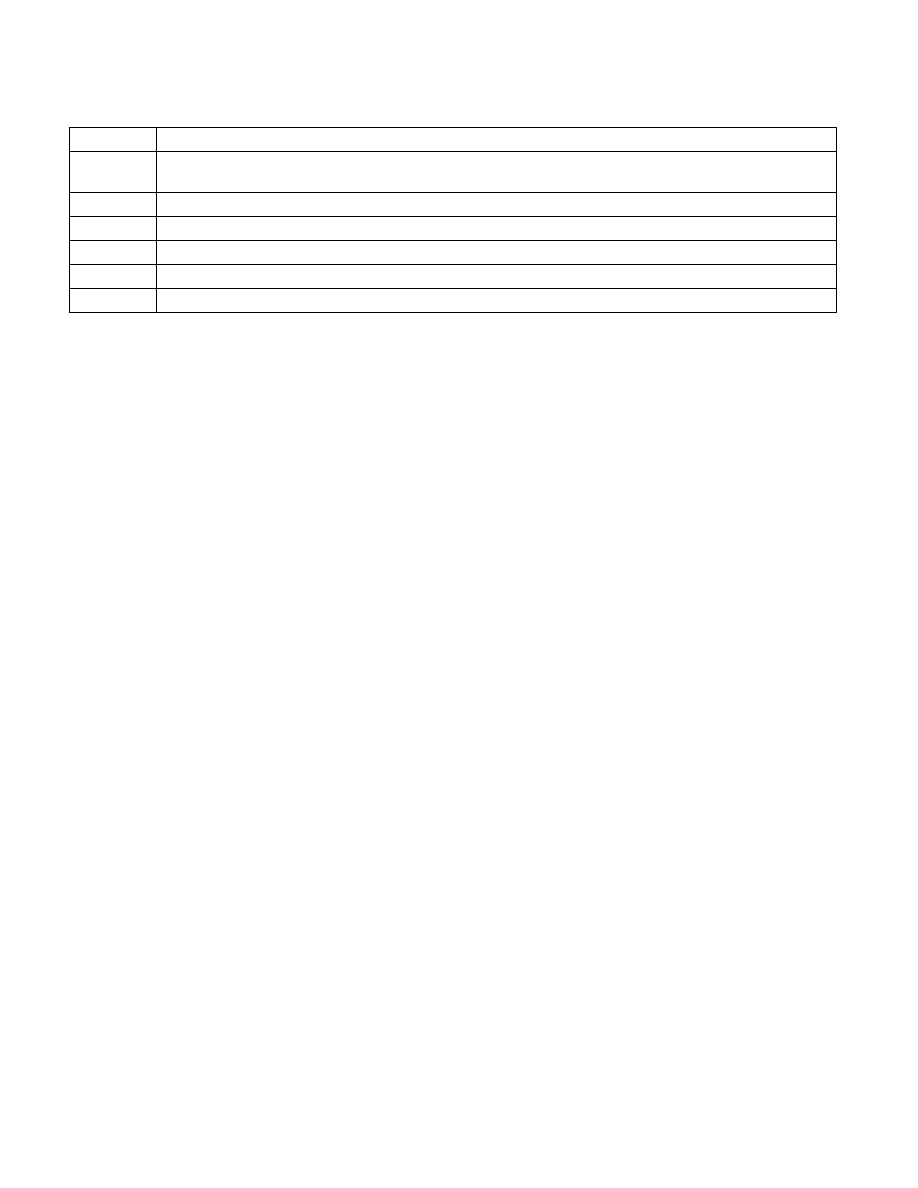

Table 6-8. SIMD Floating-Point Exceptions Priority

Priority

Description

1 (Highest)

Invalid operation exception due to SNaN operand (or any NaN operand for maximum, minimum, or certain compare and

convert operations).

2

QNaN operand

1

.

3

Any other invalid operation exception not mentioned above or a divide-by-zero exception

2

.

4

Denormal operand exception

2

.

5

Numeric overflow and underflow exceptions possibly in conjunction with the inexact result exception

2

.

6 (Lowest)

Inexact result exception.

NOTES:

1. Though a QNaN this is not an exception, the handling of a QNaN operand has precedence over lower priority exceptions. For exam-

ple, a QNaN divided by zero results in a QNaN, not a divide-by-zero- exception.

2. If masked, then instruction execution continues, and a lower priority exception can occur as well.