Vol. 3D 43-7

ENCLAVE CODE DEBUG AND PROFILING

43.5.2.3 Mispredict Bit, Record Type, and Filtering

All branch records resulting from Intel SGX instructions/AEXs are reported as predicted branches, and conse-

quently, bit 63 of MSR_LASTBRANCH_n_FROM_IP for such records is set. Branch records due to these Intel SGX

operations are always non-HLE/non-RTM records.

EENTER, ERESUME, EEXIT, and AEX are considered to be far branches. Consequently, bit 8 in MSR_LBR_SELECT

controls filtering of the new records introduced by Intel SGX.

43.6

INTERACTION WITH PERFORMANCE MONITORING

43.6.1 IA32_PERF_GLOBAL_STATUS

Enhancement

On processors supporting Intel SGX, the IA32_PERF_GLOBAL_STATUS MSR provides a bit indicator, known as “Anti

Side-channel Interference” (ASCI) at bit position 60. If this bit is 0, the performance monitoring data in various

performance monitoring counters are accumulated normally as defined by relevant architectural/microarchitec-

tural conditions. If the ASCI bit is set, the contents in various performance monitoring counters can be affected by

the direct or indirect consequence of Intel SGX protection of enclave code executing in the processor.

43.6.2

Performance Monitoring with Opt-in Entry

An opt-in enclave entry allow performance monitoring logic to observe the contribution of enclave code executing

in the processor. Thus the contents of performance monitoring counters does not distinguish between contribution

originating from enclave code or otherwise. All counters, events, precise events, etc. continue to work as defined

in the IA32/Intel 64 Software Developer Manual. Consequently, bit 60 of IA32_PERF_GLOBAL_STATUS MSR is not

set.

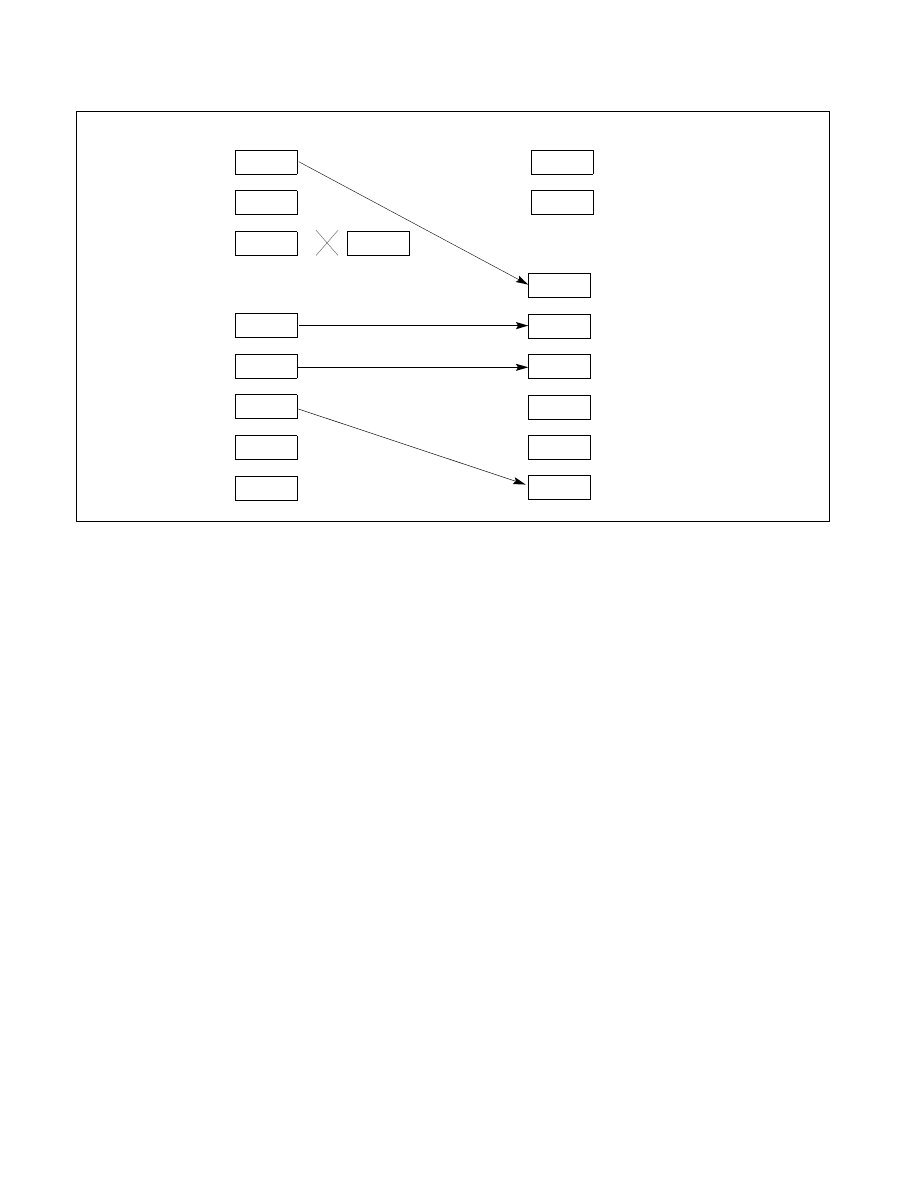

Figure 43-4. LBR Stack Interaction with Opt-out Entry

Inst1

BR2

Inst3

EEXIT

Inst4

AEP

EENTER

IRET

OS

Inst4

AEP

AEP

ERESUME

BR5

Inst6

Inst7

Fault