41-100 Vol. 3D

SGX INSTRUCTION REFERENCES

•

On opt-out entry, a number of performance monitoring counters and behaviors are modified or suppressed (see

Section 43.2.3):

— All performance monitoring activity on the current thread is suppressed except for incrementing and firing

of FIXED_CTR1 and FIXED_CTR2.

— PEBS is suppressed.

— AnyThread counting on other threads is demoted to MyThread mode and IA32_PERF_GLOBAL_STATUS[60]

on that thread is set.

— If the opt-out entry on a hardware thread results in suppression of any performance monitoring, then the

processor sets IA32_PERF_GLOBAL_STATUS[60] and IA32_PERF_GLOBAL_STATUS[63].

Concurrency Restrictions

Operation

Temp Variables in ERESUME Operational Flow

TMP_MODE64 ((IA32_EFER.LMA = 1) && (CS.L = 1));

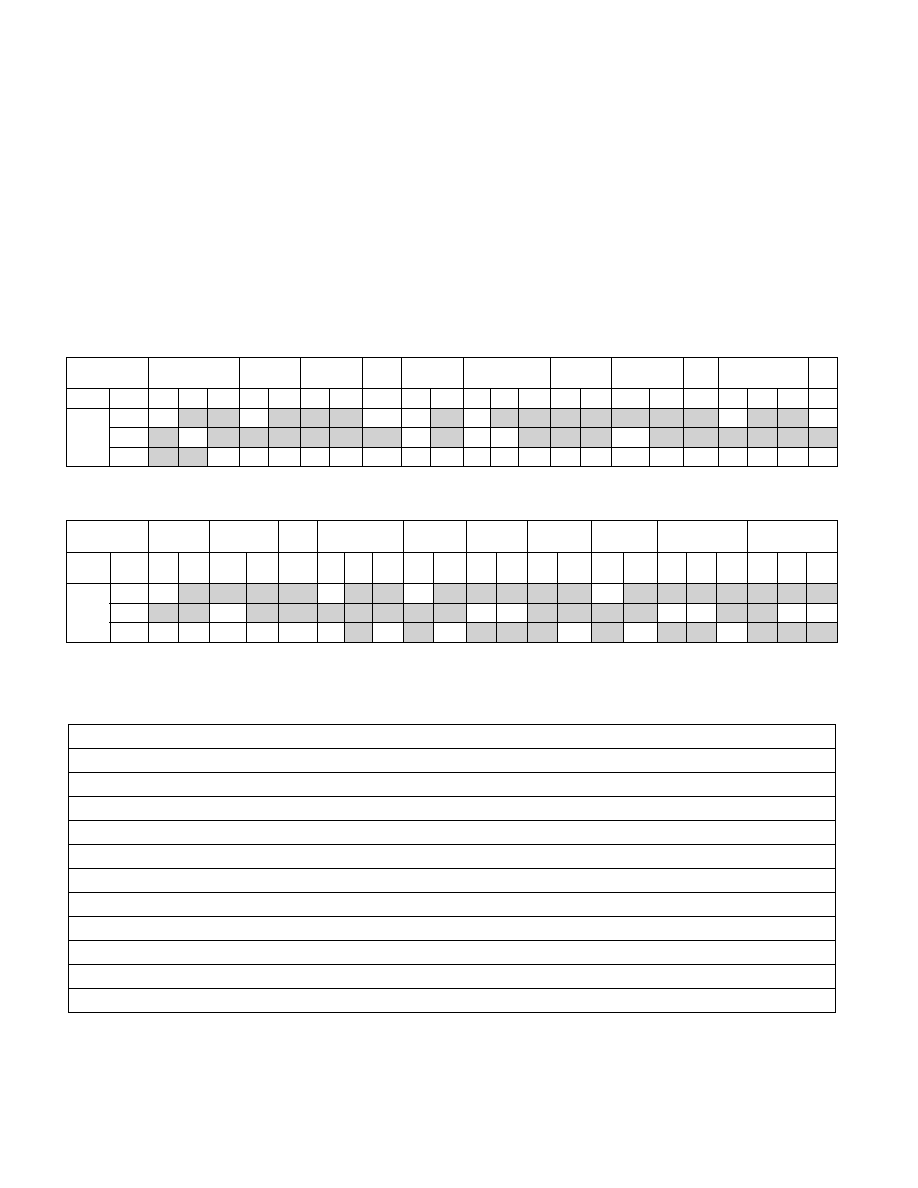

Table 41-64. Concurrency Restrictions of ERESUME with Intel® SGX Instructions - 1of 2

Operation

EEXIT

EADD

EBLOCK

ECRE

ATE

EDBGRD/

WR

EENTER/

ERESUME

EEXTEND

EGETKEY

EINIT

ELDB/ELDU

EPA

Param Targ VA

SECS Targ SECS Targ SECS SECS

Targ SECS TCS SSA SECS Targ SECS Param SECS SECS Targ VA

SECS VA

ERESU

ME

TCS

N

N

N

Y

N

N

N

SSA

U

Y

Y

U

U

SECS

Y

Y

N

Y

Y

Y

Y

Y

Y

Y

Y

Y

N

Y

Y

N

Y

Y

Y

Y

Table 41-65. Concurrency Restrictions of ERESUME with Intel® SGX Instructions - 2 of 2

Operation

EREMOVE

EREPORT

ETRA

CK

EWB

EAUG

EMODPE

EMODPR

EMODT

EACCEPT

EACCEPTCOPY

Param Targ SECS Param SECS SECS

SRC VA

SECS Targ SECS Targ SECI

NFO

Targ SECS Targ SECS Targ SECI

NFO

SECS Targ SRC SECI

NFO

ERESU

ME

TCS

N

N

N

N

SSA

U

Y

U

Y

U

U

U

SECS

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Name

Type

Size

Description

TMP_FSBASE

Effective Address

32/64

Proposed base address for FS segment.

TMP_GSBASE

Effective Address

32/64

Proposed base address for FS segment.

TMP_FSLIMIT

Effective Address

32/64

Highest legal address in proposed FS segment.

TMP_GSLIMIT

Effective Address

32/64

Highest legal address in proposed GS segment.

TMP_TARGET

Effective Address

32/64

Address of first instruction inside enclave at which execution is to resume.

TMP_SECS

Effective Address

32/64

Physical address of SECS for this enclave.

TMP_SSA

Effective Address

32/64

Address of current SSA frame.

TMP_XSIZE

integer

64

Size of XSAVE area based on SECS.ATTRIBUTES.XFRM.

TMP_SSA_PAGE

Effective Address

32/64

Pointer used to iterate over the SSA pages in the current frame.

TMP_GPR

Effective Address

32/64

Address of the GPR area within the current SSA frame.

TMP_BRANCH_RECORD

LBR Record

From/to addresses to be pushed onto the LBR stack.