41-66 Vol. 3D

SGX INSTRUCTION REFERENCES

Operation

Temp Variables in EACCEPT Operational Flow

IF (DS:RBX is not 64Byte Aligned)

THEN #GP(0); FI;

IF (DS:RBX is not within CR_ELRANGE)

THEN #GP(0); FI;

IF (DS:RBX does not resolve within an EPC)

THEN #PF(DS:RBX); FI;

IF ( (EPCM(DS:RBX &~FFFH).VALID = 0) or (EPCM(DS:RBX &~FFFH).R = 0) or (EPCM(DS:RBX &~FFFH).PENDING ≠ 0) or

(EPCM(DS:RBX &~FFFH).MODIFIED ≠ 0) or (EPCM(DS:RBX &~FFFH).BLOCKED ≠ 0) or

(EPCM(DS:RBX &~FFFH).PT ≠ PT_REG) or (EPCM(DS:RBX &~FFFH).ENCLAVESECS ≠ CR_ACTIVE_SECS) or

(EPCM(DS:RBX &~FFFH).ENCLAVEADDRESS ≠ (DS:RBX & FFFH)) )

THEN #PF(DS:RBX); FI;

(* Copy 64 bytes of contents *)

SCRATCH_SECINFO DS:RBX;

(* Check for mis-configured SECINFO flags*)

IF (SCRATCH_SECINFO reserved fields are not zero ) )

THEN #GP(0); FI;

IF (DS:RCX is not 4KByte Aligned)

THEN #GP(0); FI;

IF (DS:RCX is not within CR_ELRANGE)

THEN #GP(0); FI;

EACCE

PT

Targ

C

Y

Y

C

Y

Y

SECINFO

U

Y

U

U

SECS

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

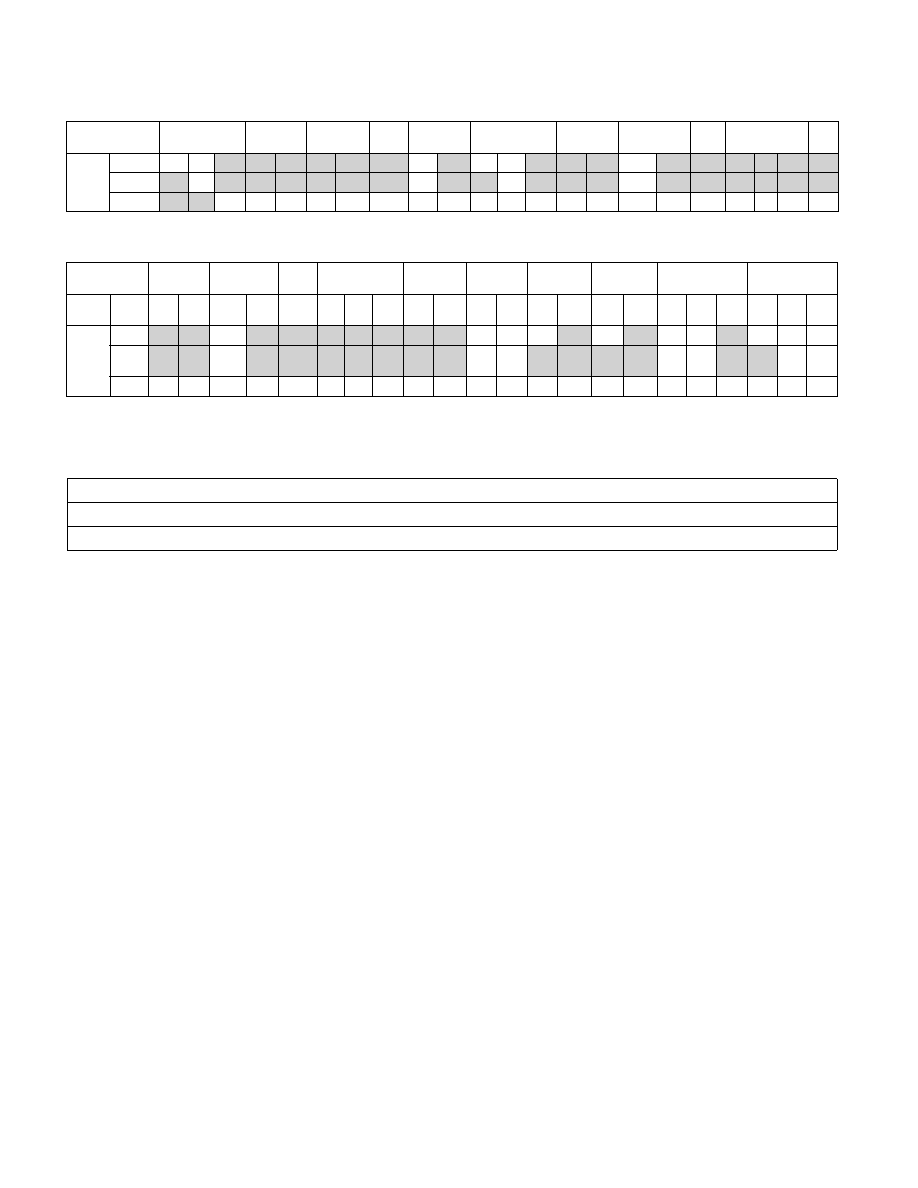

Table 41-48. Concurrency Restrictions of EACCEPT with Intel® SGX Instructions - 2 of 2

Operation

EREMOVE

EREPORT

ETRA

CK

EWB

EAUG

EMODPE

EMODPR

EMODT

EACCEPT

EACCEPTCOPY

Param Targ SECS Param SECS SECS

SRC VA

SECS Targ SECS Targ SECI

NFO

Targ SECS Targ SECS Targ SECI

NFO

SECS Targ SRC SECI

NFO

EACCE

PT

Targ

Y

N

Y

N

N

N

Y

N

Y

C

SECIN

FO

U

Y

Y

Y

Y

U

Y

SECS

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Name

Type

Size (bits)

Description

TMP_SECS

Effective Address

32/64

Physical address of SECS to which EPC operands belongs.

SCRATCH_SECINFO

SECINFO

512

Scratch storage for holding the contents of DS:RBX.

Table 41-47. Concurrency Restrictions of EACCEPT with Intel® SGX Instructions - 1of 2

Operation

EEXIT

EADD

EBLOCK

ECRE

ATE

EDBGRD/

WR

EENTER/

ERESUME

EEXTEND

EGETKEY

EINIT

ELDB/ELDU

EPA