41-60 Vol. 3D

SGX INSTRUCTION REFERENCES

Operation

Temp Variables in EWB Operational Flow

IF ( (DS:RBX is not 32Byte Aligned) or (DS:RCX is not 4KByte Aligned) )

THEN #GP(0); FI;

IF (DS:RCX does not resolve within an EPC)

THEN #PF(DS:RCX); FI;

IF (DS:RDX is not 8Byte Aligned)

THEN #GP(0); FI;

IF (DS:RDX does not resolve within an EPC)

THEN #PF(DS:RDX); FI;

(* EPCPAGE and VASLOT should not resolve to the same EPC page*)

IF (DS:RCX and DS:RDX resolve to the same EPC page)

THEN #GP(0); FI;

TMP_SRCPGE DS:RBX.SRCPGE;

(* Note PAGEINFO.PCMD is overlaid on top of PAGEINFO.SECINFO *)

TMP_PCMD DS:RBX.PCMD;

If (DS:RBX.LINADDR ≠ 0) OR (DS:RBX.SECS ≠ 0)

THEN #GP(0); FI;

IF ( (DS:TMP_PCMD is not 128Byte Aligned) or (DSTMP_SRCPGE is not 4KByte Aligned) )

THEN #GP(0); FI;

(* Check for concurrent Intel SGX instruction access to the page *)

IF (Other Intel SGX instruction is accessing page)

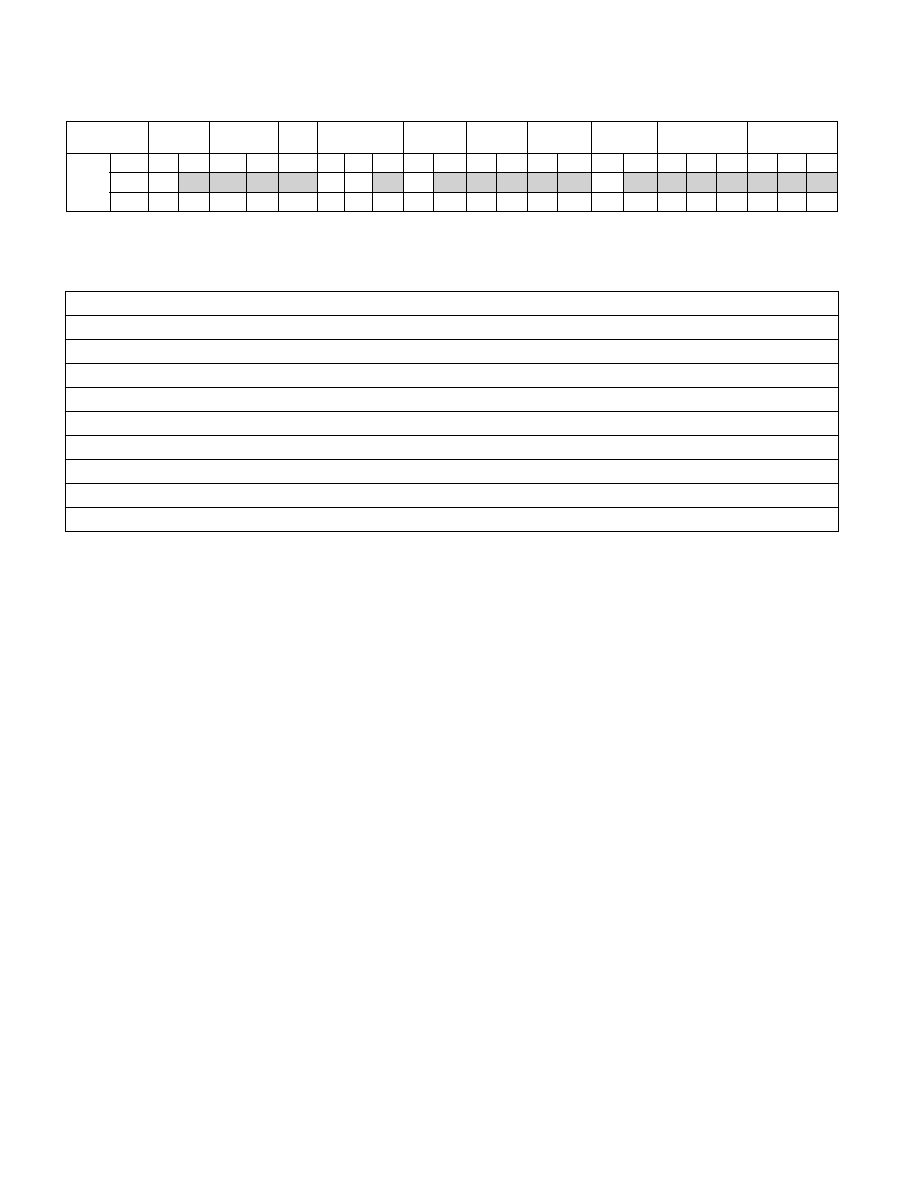

EWB

Src

N

C

C

C

N

N

N

C

N

N

C

C

N

C

N

C

C

C

C

C

C

C

VA

N

N

Y

N

N

SECS

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Name

Type

Size (Bytes) Description

TMP_SRCPGE

Memory page

4096

TMP_PCMD

PCMD

128

TMP_SECS

SECS

4096

TMP_BPEPOCH

UINT64

8

TMP_BPREFCOUNT

UINT64

8

TMP_HEADER

MAC Header

128

TMP_PCMD_ENCLAVEID

UINT64

8

TMP_VER

UINT64

8

TMP_PK

UINT128

16

Table 41-45. Concurrency Restrictions of EWB with Intel® SGX Instructions - 2 of 2

Operation

EREMOVE

EREPORT

ETRA

CK

EWB

EAUG

EMODPE

EMODPR

EMODT

EACCEPT

EACCEPTCOPY