Vol. 3D 41-59

SGX INSTRUCTION REFERENCES

EWB—Invalidate an EPC Page and Write out to Main Memory

Instruction Operand Encoding

Description

This leaf function

copies a page from the EPC to regular main memory. As part of the copying process, the page is

cryptographically protected. This instruction can only be executed when current privilege level is 0.

The table below provides additional information on the memory parameter of EPA leaf function.

EWB Memory Parameter Semantics

The error codes are:

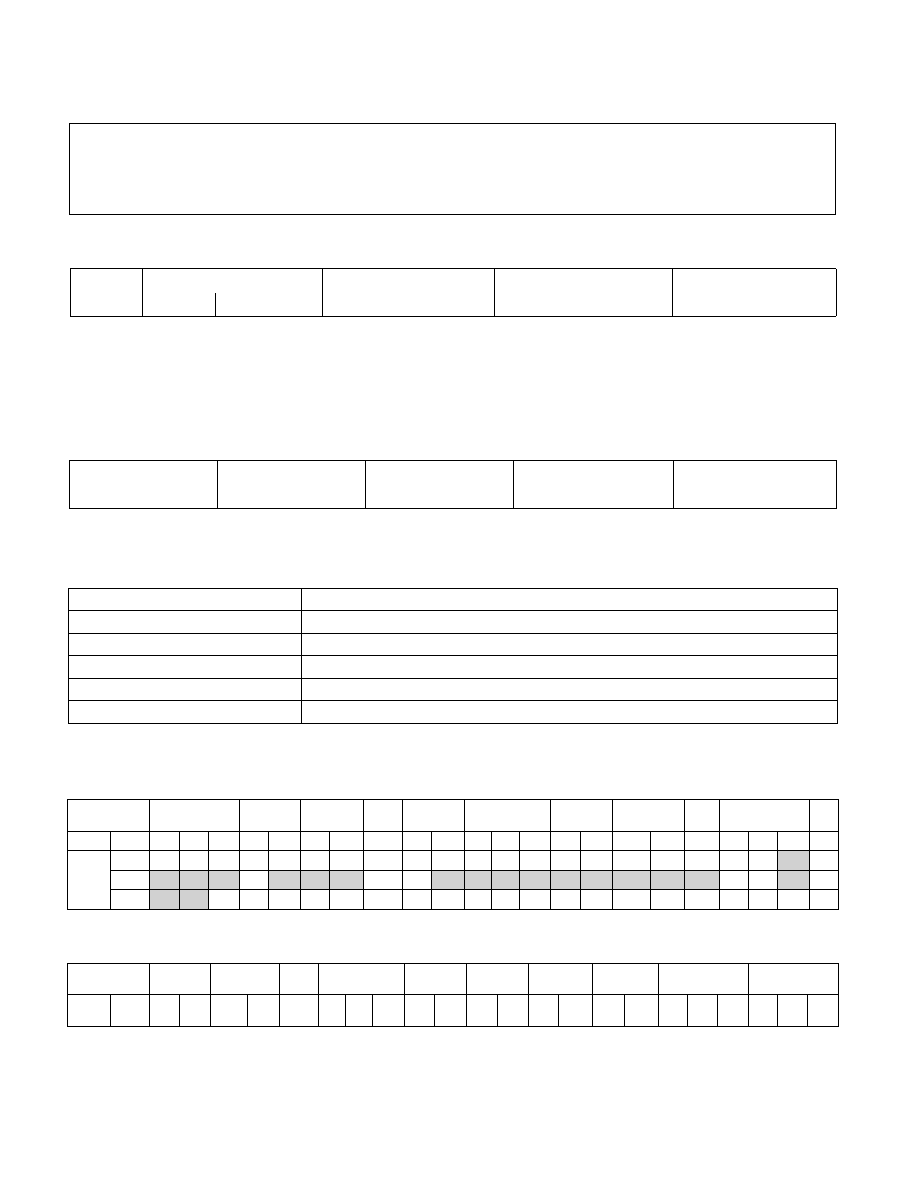

Concurrency Restrictions

Opcode/

Instruction

Op/En

64/32

bit Mode

Support

CPUID

Feature

Flag

Description

EAX = 0BH

IR

V/V

SGX1

This leaf function invalidates an EPC page and writes it out to

main memory.

ENCLS[EWB]

Op/En

EAX

RBX

RCX

RDX

IR

EWB (In)

Error code (Out) Address of an PAGEINFO (In) Address of the EPC page (In)

Address of a VA slot (In)

PAGEINFO

PAGEINFO.SRCPGE

PAGEINFO.PCMD

EPCPAGE

VASLOT

Non-EPC R/W access

Non-EPC R/W access

Non-EPC R/W access

EPC R/W access

EPC R/W access

Table 41-43. EWB Return Value in RAX

Error Code (see Table 41-3)

Description

No Error

EWB successful

SGX_PAGE_NOT_BLOCKED

If page is not marked as blocked

SGX_NOT_TRACKED

If EWB is racing with ETRACK instruction

SGX_VA_SLOT_OCCUPIED

Version array slot contained valid entry

SGX_CHILD_PRESENT

Child page present while attempting to page out enclave

Table 41-44. Concurrency Restrictions of EWB with Intel® SGX Instructions - 1of 2

Operation

EEXIT

EADD

EBLOCK

ECRE

ATE

EDBGRD/

WR

EENTER/

ERESUME

EEXTEND

EGETKEY

EINIT

ELDB/ELDU

EPA

Param Targ VA

SECS Targ SECS Targ SECS SECS

Targ SECS TCS SSA SECS Targ SECS Param SECS SECS Targ VA

SECS VA

EWB

Src

C

C

C

N

N

N

C

N

N

C

N

C

C

N

C

C

C

N

N

N

N

VA

N

N

Y

N

Y

N

SECS

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Table 41-45. Concurrency Restrictions of EWB with Intel® SGX Instructions - 2 of 2

Operation

EREMOVE

EREPORT

ETRA

CK

EWB

EAUG

EMODPE

EMODPR

EMODT

EACCEPT

EACCEPTCOPY

Param Targ SECS Param SECS SECS

SRC VA

SECS Targ SECS Targ SECI

NFO

Targ SECS Targ SECS Targ SECI

NFO

SECS Targ SRC SECI

NFO