Vol. 3D 41-55

SGX INSTRUCTION REFERENCES

Concurrency Restrictions

Operation

Temp Variables in EREMOVE Operational Flow

IF (DS:RCX is not 4KByte Aligned)

THEN #GP(0); FI;

IF (DS:RCX does not resolve to an EPC page)

THEN #PF(DS:RCX); FI;

TMP_SECS Get_SECS_ADDRESS();

(* Check the EPC page for concurrency *)

IF (EPC page being referenced by another Intel SGX instruction)

THEN #GP(0); FI;

(* if DS:RCX is already unused, nothing to do*)

IF ( (EPCM(DS:RCX).VALID = 0) or (EPCM(DS:RCX).PT = PT_TRIM AND EPCM(DS:RCX).MODIFIED = 0))

THEN GOTO DONE;

FI;

IF (EPCM(DS:RCX).PT = PT_VA)

THEN

EPCM(DS:RCX).VALID 0;

GOTO DONE;

FI;

IF (EPCM(DS:RCX).PT = PT_SECS)

THEN

IF (DS:RCX has an EPC page associated with it)

THEN

RFLAGS.ZF 1;

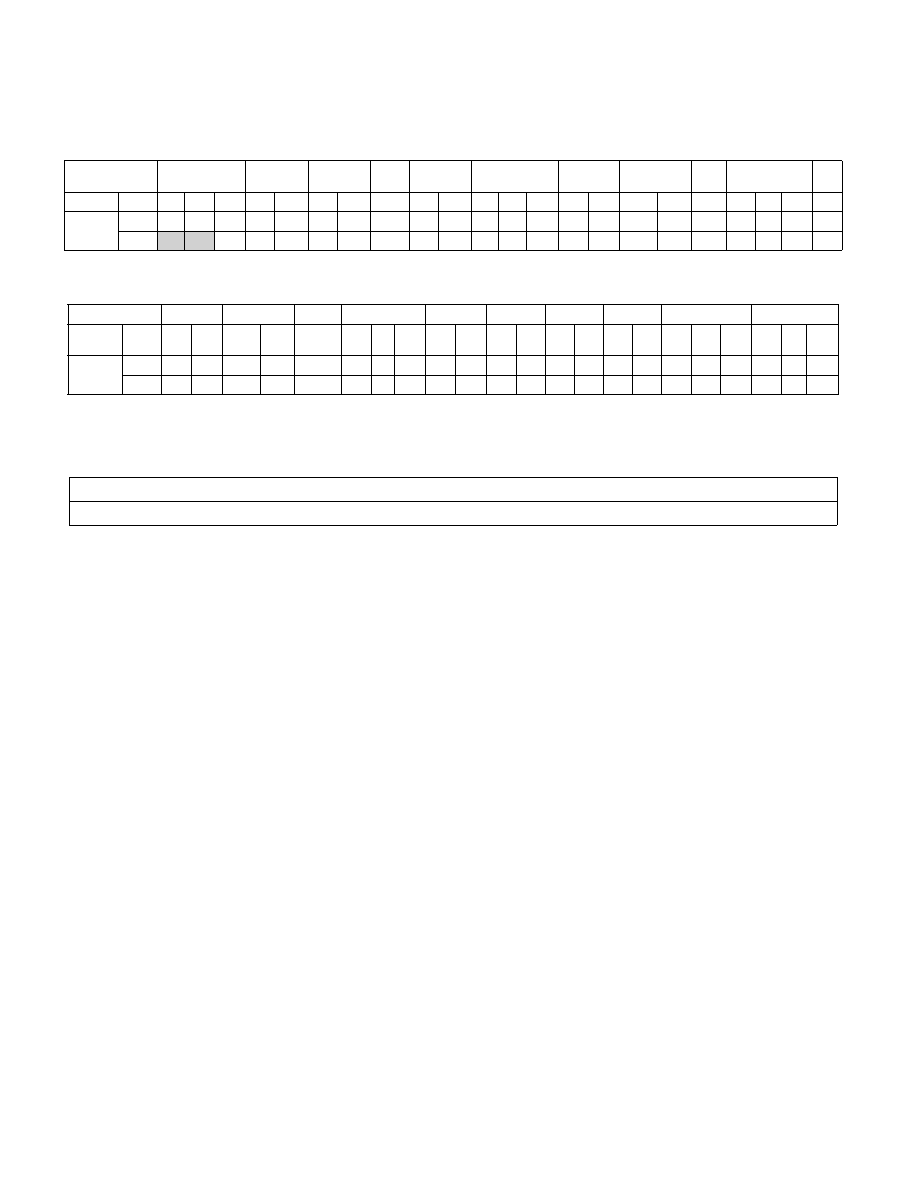

Table 41-37. Concurrency Restrictions of EREMOVE with Other Intel® SGX Operations 1 of 2

Operation

EEXIT

EADD

EBLOCK

ECRE

ATE

EDBGRD/

WR

EENTER/

ERESUME

EEXTEND

EGETKEY

EINIT

ELDB/ELDU

EPA

Param TCS SSA SECS Targ SECS Targ SECS SECS

Targ SECS TCS SSA SECS Targ SECS Param SECS SECS Targ VA

SECS VA

EREMOVE Targ

C

C

C

N

N

N

C

N

N

C

N

C

C

N

C

C

C

N

N

N

N

N

SECS

C

Y

Y

Y

Y

Y

Y

Y

Y

Y

C

Y

Y

Y

C

Y

Y

Y

Y

Y

Table 41-38. Concurrency Restrictions of EREMOVE with Other Intel® SGX Operations 2 of 2

Operation

EREMOVE

EREPORT

ETRACK

EWB

EAUG

EMODPE

EMODPR

EMODT

EACCEPT

EACCEPTCOPY

Param Targ SECS Param SECS SECS

SRC VA SECS Targ SECS Targ SECI

NFO

Targ SEC

S

Targ SEC

S

Targ SECI

NFO

SECS Targ SR

C

SECI

NFO

EREMOVE Targ

N

C

C

C

N

N

N

C

N

N

C

C

N

C

N

C

C

C

C

C

C

C

SECS

Y

Y

Y

C

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

C

C

C

Y

Y

Y

Name

Type

Size (Bits)

Description

TMP_SECS

Effective Address

32/64

Effective address of the SECS destination page.